#### UNIVERSITY OF CASSINO AND SOUTHERN LAZIO

## Ph.D. Program in

### Methods, Models and Technologies for Engineering

Curriculum Electrical Engineering

Cycle XXXV

# Analysis and Modeling of a 650 V GaN-based Half Bridge during Short Circuit operation

SSD: ING-INF/01

*Ph.D. Program Coordinator* Prof. Fabrizio Marignetti

*Ph.D. candidate* Simone Palazzo

Supervisor Prof. Giovanni Busatto

# Acknowledgements

The three years of my Ph. D. have been the most intense, challenging and gratifying of my life and I would like to thank all the people who shared this journey with me. First of all, I wish to thank my supervisor, prof. Giovanni Busatto, for believing in me since the first day I met him. He helped me a lot in finding my way and gave me the opportunity to grow, both technically and humanely. He is an important guide for me and for our group and I hope we will share many more days together in the laboratory. I also thank the other professors of the electronics group, Nunzia and Francesco, for their valuable support, suggestions and recommendations.

I wish to thank the company Rete Ferroviaria Italiana s.p.a. for giving me the opportunity to undertake the Ph. D. and for funding it during the three years. For this, I must especially thank my friend and colleague eng. Dario Di Ruzza, who strongly helped and encouraged me during these years: I owe him a lot, and not only for the Ph. D. ...

I also wish to thank my colleagues of the Industrial Electronics Laboratory who worked with me over these years, in particular Enzo, Emanuele, Daniele, Roberto, Luca and all the other colleagues I was lucky to meet. I would also like to thank the coordinator of the Ph. D. program, prof. Fabrizio Marignetti, for his unlimited availability and support.

I want to thank my friends Antonio and Emanuele, with whom I shared all the years of the university and also the Ph. D.. I feel lucky to have such friends and colleagues who inspire me to do better and better.

I am also grateful for the time I spent in Kiel, Germany, where I completed part of my PhD. I felt honored to cooperate with the amazing group of the Chair of Power Electronics, and I deeply thank prof. Marco Liserre for hosting me there and giving me the opportunity to touch the cutting edges of power electronics. I also wish to thank the friends I found in Kiel, who made me feel like at home.

Special thanks to my closest friends, Andrea, Giuseppe and Gianpaolo, who are a constant presence in my life and with whom I have spent the best moments and experiences.

I want to thank my whole family, which means everything to me, and especially my brother Luca and my parents: I will try to follow your teachings and make you proud for the rest of my life. Thank you for your constant support, suggestions and most of all for the love you give me, that I hope to return to you despite my not very expansive nature!

I would like to thank Giulia. You have been essential over these years and I thank you for your constant presence, strength, support and motivation. I would not have made it through this arduous experience without you. You are the most important person in my life, your love means everything to me and makes me a better person.

Finally, thank you to all the people I met over these years, each of you has played a special role in my life and I am grateful for that.

Thank you all!

Cassino, 2023

Simone

# **Abstract**

Following the vision of a green and sustainable future, the use of Wide Band Gap (WBG) semiconductors in Power Electronics is of paramount importance, since their physical properties enable the achievement of the highest performances in the energy conversion processes in terms of efficiency and power density. Silicon Carbide (SiC) power MOSFETs are now the leaders of the industrial, renewable and automotive markets thanks to their wide range of breakdown voltages (650-, 1200-, 1700-V), low onresistance and fast switching times. At the same time, they offer excellent performances in terms of robustness and reliability, key features for all commercial applications. However, SiC MOSFETs seem to have reached their technological limit, while even better performances can be reached using Gallium Nitride High Electron Mobility Transistors (GaN HEMTs), which have attracted significant interest in the industrial and academic communities in recent years. Even if GaN transistors were born as normally-on devices, finding space in radio- and audio-frequency applications, the possibility to obtain power devices with very low on-resistance and extremely fast switching characteristics has prompted the development of normally-off GaN devices for power applications. However, the lateral structure limits the maximum breakdown voltage to 650 V, while the lower thermal conductivity forces the operating temperature to be lower than 150 °C. Furthermore, the reliability and the Short Circuit (SC) robustness of GaN HEMTs are lower in comparison to SiC and Si devices, strongly reducing their advantages and preventing their widespread use in commercial applications.

In this perspective, this thesis focuses on the SC operation of a 650 V GaN-based Half Bridge (HB), evaluating the influence of various operating parameters, including the DC-link voltage and the gate resistance. The SC characterizations presented in the literature focus on a single device, often operating in conditions far from the real application, e.g. with a large gate resistor. The study proposed in this thesis investigates the real case of the SC operation of a HB, determining the impact that another identical device can have on the SC and the interactions between the two GaN HEMTs. From a comparative analysis of experimental results in the literature and preliminary simulation results, significant differences are noticed, leading towards the development of a model for the drain and gate current of the GaN HEMT under study. After designing and realizing a prototype test board, an I – V characterization is performed for the drain and gate current, whose results are used to derive simple behavioral models for both drain and gate currents, achieving good accuracy. The behavioral model developed for the GaN HEMT, suitable for both

nominal operating conditions and SC operation, is integrated with the manufacturer's LTSpice model and used to accurately simulate the behavior of the devices during the SC, giving also the possibility to determine the impact of the gate leakage current on the self-regulation mechanism of the SC current. Experimental SC tests are led on the realized board, confirming the theoretical analysis and highlighting the effects of the DC-link voltage, the impact of using large gate resistance and the presence of mismatches in the circuit of the two transistors. Moreover, the SC power and energy are computed and a temperature estimation is provided for both devices to evaluate the different electrothermal stress on the GaN HEMTs. The proposed model is validated by comparing the LTSpice simulations with the experimental results in all the tested conditions. Finally, the possibility to exploit the proposed gate leakage current model to estimate the junction temperature of the GaN HEMT is investigated and is verified evaluating the temperature reached by the devices during the SC event.

# **Abstract**

(Italiano)

Seguendo la visione di un futuro verde e sostenibile, l'uso di semiconduttori di tipo Wide Band Gap (WBG) nell'elettronica di potenza è di fondamentale importanza, poiché le loro proprietà fisiche consentono di ottenere le massime prestazioni nella conversione di energia in termini di efficienza e densità di potenza. I MOSFET di potenza al carburo di silicio (SiC) sono oggi i leader dei mercati industriali, delle energie rinnovabili e dell'automotive grazie alla loro ampia gamma di tensioni di bloccaggio (650-, 1200-, 1700- V), alla bassa resistenza in *on* e ai rapidi tempi di commutazione. Allo stesso tempo, offrono prestazioni eccellenti in termini di robustezza e affidabilità, caratteristiche fondamentali per tutte le applicazioni commerciali. Tuttavia, i MOSFET in SiC sembrano aver raggiunto il loro limite tecnologico, mentre prestazioni ancora migliori possono essere ottenute con i transistor ad alta mobilità elettronica al nitruro di gallio (GaN HEMT), che negli ultimi anni hanno suscitato un notevole interesse nella comunità industriale e accademica. Anche se i transistor in GaN sono nati come dispositivi normalmente accesi, trovando spazio nelle applicazioni di radio- e audio-frequenza, la possibilità di ottenere dispositivi di potenza con una resistenza in on molto bassa e caratteristiche di commutazione estremamente veloci ha spinto lo sviluppo di dispositivi in GaN normalmente spenti per applicazioni di potenza. Tuttavia, la loro struttura laterale limita la tensione massima di bloccaggio a 650 V, mentre la minore conducibilità termica costringe una temperatura di esercizio inferiore a 150 °C. Inoltre, l'affidabilità e la resistenza al cortocircuito (SC) degli HEMT sono inferiori rispetto ai dispositivi in SiC e Si, riducendo fortemente i loro vantaggi e impedendone l'uso diffuso nelle applicazioni commerciali.

In quest'ottica, il presente lavoro di tesi si concentra sul funzionamento in cortocircuito di un Half Bridge (HB) con dispositivi in GaN da 650 V, valutando l'influenza di vari parametri operativi, tra cui la tensione del DC-link e la resistenza di gate. Le caratterizzazioni in cortocircuito presentate in letteratura si concentrano su un singolo dispositivo, spesso operante in condizioni lontane dall'applicazione reale, ad esempio con una grande resistenza di gate. Lo studio proposto in questa tesi indaga il caso reale del funzionamento in cortocircuito di un HB, determinando l'impatto che può avere un altro dispositivo identico e le interazioni tra i due HEMT. Da un'analisi comparativa dei risultati sperimentali presenti in letteratura e dei risultati preliminari delle simulazioni, si notano differenze significative che hanno condotto allo sviluppo di un modello per la corrente di drain e di gate dell'HEMT oggetto di studio. Dopo aver progettato e realizzato

un prototipo per i test, è stata eseguita una caratterizzazione I - V per la corrente di drain e di gate, i cui risultati sono stati utilizzati per ricavare semplici modelli comportamentali per entrambe le correnti di drain e di gate, ottenendo una buona accuratezza.

Il modello comportamentale sviluppato per l'HEMT in GaN, adatto sia alle condizioni operative nominali che al funzionamento in cortocircuito, viene integrato con il modello LTSpice del produttore e utilizzato per simulare accuratamente il comportamento dei dispositivi durante il cortocircuito, dando anche la possibilità di determinare l'impatto della corrente di leakage di gate sul meccanismo di autoregolazione della corrente di cortocircuito. I test sperimentali in cortocircuito sono condotti sulla scheda realizzata, confermando l'analisi teorica ed evidenziando gli effetti della tensione del bus DC, l'impatto dell'utilizzo di una grande resistenza di gate e la presenza di differenze nel circuito dei due transistor. Inoltre sono calcolate la potenza e l'energia in cortocircuito ed è fornita una stima della temperatura per entrambi i dispositivi per valutare il diverso stress elettrotermico sugli HEMT. Il modello proposto è validato confrontando le simulazioni LTSpice con i risultati sperimentali in tutte le condizioni di test. Infine, viene studiata la possibilità di sfruttare il modello proposto per la corrente di leakage di gate per stimare la temperatura di giunzione dell'HEMT e viene verificata stimando la temperatura raggiunta dai dispositivi durante il cortocircuito.

# **Table of Contents**

| 1 | Ove   | rview on GaN HEMTs                             | 5    |

|---|-------|------------------------------------------------|------|

|   | 1.1   | Introduction                                   | 5    |

|   | 1.2   | Thesis outline                                 | 7    |

|   | 1.3   | Research contributions                         | 8    |

|   | 1.4   | GaN HEMTs in Power Electronics.                | 9    |

|   | 1.4.1 | Basic structures                               | .11  |

|   | 1.4.2 | 2 Electrical characteristics                   | . 12 |

|   | 1.4.3 | 8 Capacitance and charge                       | . 15 |

|   | 1.4.4 | Figure of Merit                                | . 17 |

|   | 1.4.5 | Modeling of GaN HEMTs                          | . 20 |

|   | 1.4.6 | 6 Reliability aspects                          | . 24 |

|   | 1.5   | Short Circuit robustness of GaN HEMTs          | . 26 |

| 2 | Sho   | rt Circuit analysis of a GaN-based Half Bridge | .35  |

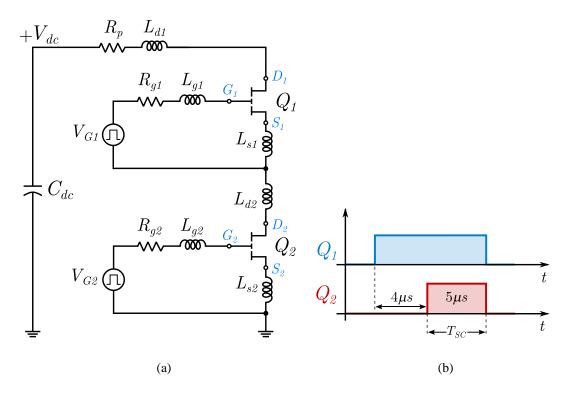

|   | 2.1   | Short Circuit operation of the Half Bridge     | .36  |

|   | 2.2   | Simulation analysis                            | .39  |

|   | 2.2.1 | Effect of DC-link voltage                      | .40  |

|   | 2.2.2 | 2 Effect of gate voltage                       | .43  |

|   | 2.2.3 | B Effect of gate resistance                    | .45  |

|   | 2.2.4 | 4 Effect of parasitic inductances              | .48  |

|   | 2.2.5 | 5 Effect of mismatch                           | .52  |

|   | 2.3   | Discussion                                          | 56         |

|---|-------|-----------------------------------------------------|------------|

| 3 | Desi  | gn and realization of a 650 V GaN-based Half Bridge | 57         |

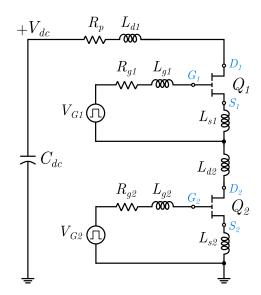

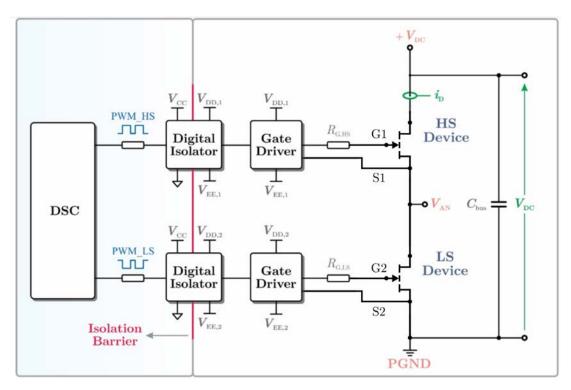

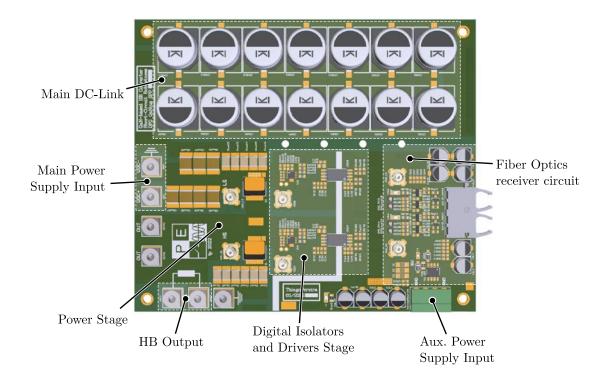

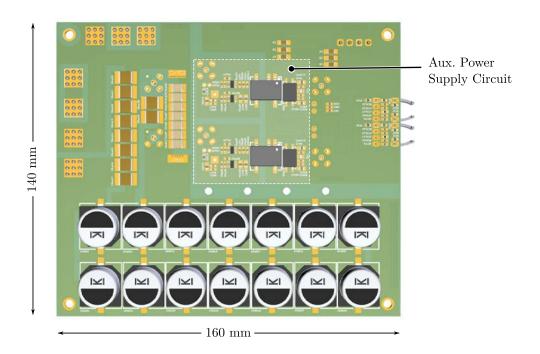

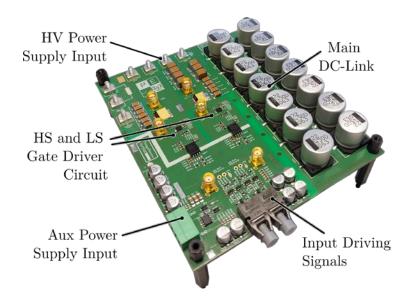

|   | 3.1   | Circuit scheme                                      | 57         |

|   | 3.2   | Design of the test board                            | 59         |

|   | 3.2.1 | Power stage                                         | 59         |

|   | 3.2.2 | 2 Bus capacitors                                    | 62         |

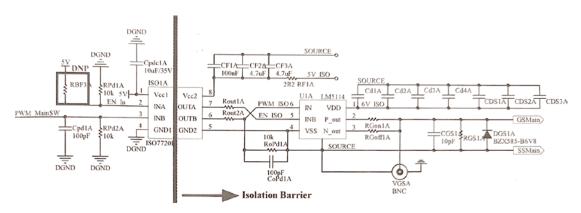

|   | 3.2.3 | B Drivers and digital isolators                     | 63         |

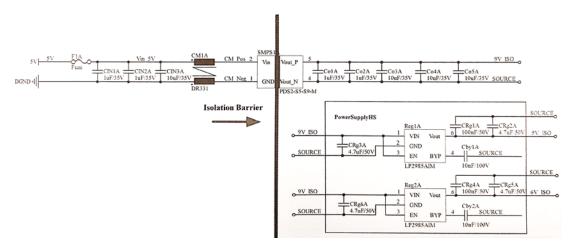

|   | 3.2.4 | 4 Auxiliary power supply                            | 66         |

|   | 3.2.5 | 5 Control board                                     | 67         |

|   | 3.2.6 | 6 Realized prototype                                | 68         |

| 4 | Mod   | leling of GaN HEMTs in Short Circuit                | 70         |

|   | 4.1   | Drain $I - V$ characterization                      | 72         |

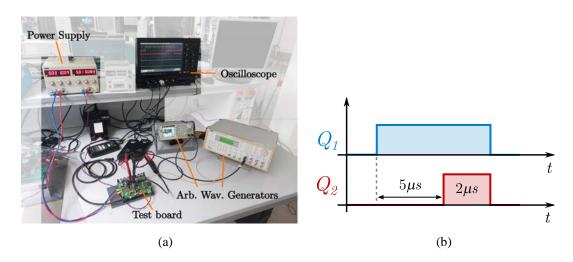

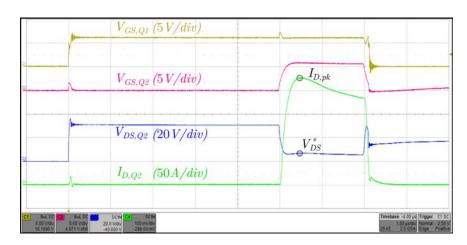

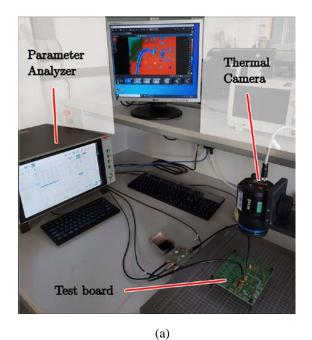

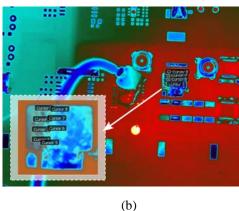

|   | 4.1.1 | Test setup                                          | 72         |

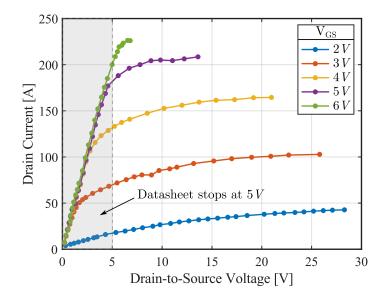

|   | 4.1.2 | Results of experimental characterization            | <b>7</b> 4 |

|   | 4.2   | Gate $I - V$ characterization                       | 76         |

|   | 4.2.1 | Test setup                                          | 77         |

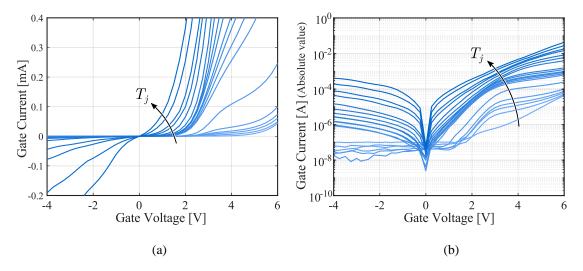

|   | 4.2.2 | Results of experimental characterization            | 78         |

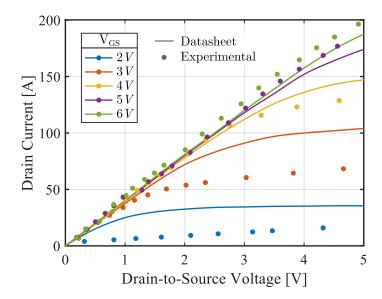

|   | 4.3   | Drain current model                                 | 80         |

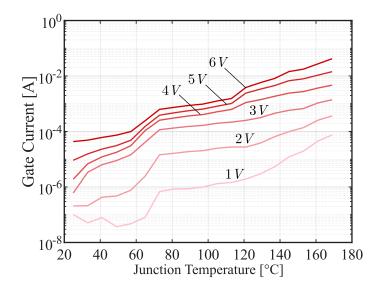

|   | 4.4   | Gate current model                                  | 85         |

|   | 4.5   | Equivalent model of the GaN HEMT                    | 89         |

| 5 | Exp   | erimental Short Circuit tests and model validation  | 93         |

|   | 5.1   | Setup description for Short Circuit tests           | 93         |

|   | 5.2   | Results with $100 \Omega$ gate resistance           | 95         |

|   | 5.2.1 | Energy and temperature estimation                   | 98         |

|   | 5 3   | Results with 22 O gate resistance                   | 101        |

| Bi | bliogra | aphy                                                  | .127  |

|----|---------|-------------------------------------------------------|-------|

|    | 6.2     | Outlooks                                              | . 125 |

|    | 6.1     | Conclusions                                           | . 121 |

| 6  | Con     | clusions and Outlooks                                 | . 121 |

|    | 5.5     | Temperature estimation through the gate leakage model | . 117 |

|    | 5.4.1   | Impact of thermal model                               | . 113 |

|    | 5.4     | Validation of the model                               | . 106 |

|    | 5.3.1   | Energy and temperature estimation                     | . 104 |

# 1 Overview on GaN HEMTs

#### 1.1 Introduction

Last generation Wide Band-Gap (WBG) power devices are finding increasing use in power electronics applications, replacing the well-established Silicon (Si) power MOSFETs and IGBTs, as they can achieve higher performances in terms of efficiency and power density. Silicon Carbide (SiC) and Gallium Nitride (GaN), thanks to their superior properties, are the most employed semiconductor materials for the realization of WBG power devices [1], [2].

SiC technology has already reached a high maturity level, enabling the possibility to operate in a wide range of power and voltage levels with high thermal stability, robustness and reliability. In fact, in the last years it has become the preferred solution for many industrial, automotive and grid-tied applications [3]-[5]. On the other hand, GaN-based transistors are in fast and promising development and are introduced as a very hard and mechanically stable semiconductor. With potential higher breakdown strength, faster switching speed, higher thermal conductivity and lower on-resistance, GaN High Electron Mobility Transistors (GaN HEMTs), significantly outperform Si-based devices and are a valuable alternative to SiC MOSFETs in lower voltage applications. GaN HEMTs enable the achievement of increasing efficiency and power density of power converters, though trying to maintain the same level of reliability reached with Si and SiC technologies [6]-[8].

Even if GaN HEMTs were initially adopted in Radio-Frequency applications, now they are also spreading in consumer electronics, data centers, audio amplification and low voltage industrial and automotive applications, such as motor drives, wireless power

transfer and on-board chargers [9]-[14], also because of the technology improvement in realizing normally-off GaN devices. In particular, GaN HEMTs are employed in many DC-DC converter topologies, both isolated, such as Flyback, DAB and resonant converters, and non-isolated as Buck, Boost and Buck-Boost [15]-[21].

Nevertheless, some factors still limit the spread of GaN HEMTs in all the fields of power electronics. They are mainly linked to the relatively low breakdown voltage and reliability and robustness issues. The first factor is dependent on the lateral structure of GaN devices, which limits the maximum breakdown voltage to about 650 V for HEMTs and 900 V for cascode devices and does not enable the avalanche capability [22], [23]. Some promising GaN transistors with a vertical structure have recently been developed in order to overcome this limitation, showing 1.2 kV breakdown voltage, avalanche capability and high robustness [24], [25], but they are still far from the commercial market and a widespread use.

The major causes of reliability issues in GaN HEMTs are related to charge trapping and hot electrons, that heavily degrade the device performances, both in its on- and off-state. The main processes related to charge trapping and hot electrons involve the dynamic on-resistance increase, the threshold voltage shift and the degradation of the gate [26]-[28]. The presence of charge traps derives from imperfections in the structure of the device, that can be induced by the realization process, and can be localized at different locations and energy levels [29]-[30]. Hot electrons can be generated by highly stressful operating conditions and the simultaneous presence of high voltage and current, as during the hard-switching event [26]-[28], [31], [32].

Moreover, another relevant issue of GaN HEMTs is linked to the Short Circuit (SC) robustness. Many studies and findings have been conducted in recent years on the SC behavior of GaN devices: from the capability, degradation and withstand time tests [33]-[36], to instability [37]-[39] and failure mechanisms analysis [40], [41]. Considering devices with 650 V breakdown voltage, GaN HEMTs show good SC ruggedness for voltages lower than 350 V, but at higher voltage they suffer of unrecoverable breakdown, showing lower SC capability in comparison with SiC and Si MOSFETs. The failure time in these conditions is less than 1 µs, making the design of a protection circuit against SC for GaN HEMTs a challenge. This is even more complicated because of the absence of a simple but reliable analytical model of the GaN HEMT that represents its behavior in SC conditions and that allows the designer to accurately predict the SC behavior without performing experimental tests and damaging the transistors, saving time and costs. Moreover, all the experimental SC tests presented in the literature are performed on a single device, sometimes connected in series to a higher current power device acting as a protection. However, in practical applications, the SC event can be triggered in Half Bridge-based topologies and involves two identical devices. The presence of two identical

GaN HEMTs during the SC event is not investigated in the literature, even if this can lead to relevant differences in the electro-thermal stress distribution between the two devices.

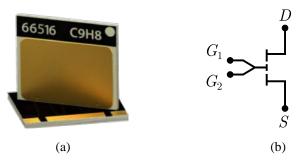

In this perspective, this thesis focuses on the Short Circuit behavior of normally-off GaN HEMTs for power converters applications. In particular, the SC operation of a Half Bridge is presented and analyzed through simulations and experimental tests. A PCB with two 650 V–60 A GaN HEMTs in Half Bridge configuration has been designed and realized to perform the I – V characterization and SC tests. A static I–V characterization of drain and gate currents has been led on the 650 V–60 A GaN HEMT at different operating conditions in order to derive a behavioral model for the drain and gate currents, suitable for the device simulation both during normal and SC operation of the device. The proposed model is used to simulate and predict the real SC behavior of the GaN devices, determining the main information about the SC event, such as the peak power dissipation, the involved energy and the junction temperature. Moreover, the model can be an useful instrument in designing a protection circuit against SC for GaN HEMTs. Experimental SC tests are performed at different bus voltages and with two values of gate resistance to validate the model and its applicability to other GaN HEMTs with different characteristics is evaluated.

#### 1.2 Thesis outline

The outline of the thesis follows this structure:

- ► Chapter 1 provides an introductive overview on the main features, the modeling approaches and the state-of-the-art of SC characterization of GaN HEMTs.

- ► Chapter 2 introduces the analysis of the SC behavior of a GaN-based Half Bridge, highlighting the main phenomena involved during the SC and evaluating the effects of many circuit parameters on the SC behavior.

- ► Chapter 3 describes the design process of the PCB used to perform all the experimental tests presented in the thesis.

- ► Chapter 4 describes the procedure adopted to perform the experimental drain and gate I V characterization and shows the obtained results on a 650 V 60 A GaN HEMT. Based on these results, a behavioral model for the drain and gate currents of the GaN HEMT is proposed. Then, the accuracy of the model is evaluated.

- ► Chapter 5 presents the implementation of the proposed model in SPICE, its comparison with the manufacturer model and its validation with experimental

results of non-destructive SC tests at different operating conditions. The model is then applied to a different GaN HEMT to evaluate its scalability and adaptability.

► Chapter 6 summarizes the main results and contributions of the thesis, finally providing the conclusion and future outlooks.

#### 1.3 Research contributions

Many research topics have been faced during the Ph.D. program, focusing on different fields of power electronics. In particular, I was devoted to the design, testing and optimization of power converters for railway applications and their integration with WBG power devices. These research activities were led in cooperation with two leading companies of the Italian railway field, such as Rete Ferroviaria Italiana (RFI s.p.a.) and Hitachi Rail. In the last part of my Ph.D. program I also focused on the robustness and the SC behavior of GaN HEMTs for their application in power converters.

The research contributions of my activity, published in international conference proceedings and scientific journals, are listed in the following.

#### **Journal Papers**

- S. A. Mortazavizadeh, S. Palazzo, A. Amendola, E. De Santis, D. Di Ruzza, G. Panariello, A. Sanseverino, F. Velardi and G. Busatto, "High Frequency, High Efficiency, and High Power Density GaN-Based LLC Resonant Converter: State-of-the-Art and Perspectives," Appl. Sci. 2021, 11, 11350. https://doi.org/10.3390/app112311350.

- C. Abbate, L. Colella, R. Di Folco, G. Busatto, E. Martano, S. Palazzo, A. Sanseverino and F. Velardi, "An Accurate Switching Current Measurement Based on Resistive Shunt Applied to Short Circuit GaN HEMT Characterization," Appl. Sci. 2021, 11, 9138. https://doi.org/10.3390/app11199138.

#### **Conference Papers**

S. Palazzo, G. Busatto, E. De Santis, R. Giacomobono, D. Di Ruzza and G. Panariello, "A Hybrid Modulation Technique for Voltage Regulation in LLC Converters in the Presence of Transformer Parasitic Capacitance," 2022 IEEE

- Energy Conversion Congress and Exposition (ECCE), 2022, 1-8, doi: 10.1109/ECCE50734.2022.9947909.

- G. Panariello, D. Di Ruzza, M. Canigliula, S. Palazzo, G. Busatto, E. De Santis, "Energy Efficient Architecture of Power Supply for Field Devices and Controllers of the RFI Computer-Based Interlocking," World Congress on Railway Research (WCRR), 2022, Birmingham, UK.

- D. Marciano, S. Palazzo, G. Busatto, A. Sanseverino and F. Velardi, "Role of Active Clamp Circuit in a DC/AC Isolated Converter based on the principle of Pulsating DC Link," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, 2704-2709, doi: 10.1109/ECCE47101.2021.9595012.

- D. Marciano, S. Palazzo et al., "A Novel Modulation Technique For Pulsating DC Link Multistage Converter With Zero Voltage Transition Based On Different And Unrelated Switching Frequencies," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, 3289-3294, doi:10.1109/ECCE47101.2021.9595973.

- G. Busatto, A. Di Pasquale, D. Marciano, S. Palazzo, A. Sanseverino, F. Velardi, "Physical mechanisms for gate damage induced by heavy ions in SiC power MOSFET," Microelectronics Reliability, vol.114, November 2020, doi:113903.

- F. Calabrò, D. Bravo, C. Carissimo, E. Di Fazio, A. Di Pasquale, A.A.M.O. Eldray, C. Fabrizi, J.G.S. Gerges, S. Palazzo, J.F.F.T. Wassef, "Null rules for the detection of lower regularity of functions," Journal of Computational and Applied Mathematics, Volume 361, 2019, 547-553, doi: 10.1016/j.cam.2019.05.002.

#### In submission

S. Palazzo, T. Pereira, Y. Pascal, G. Busatto and M. Liserre, "A Behavioral Model for Short Circuit Operation of a GaN-based Half Bridge," 2023 IEEE Energy Conversion Congress and Exposition (ECCE), 2023, digest submitted.

#### 1.4 GaN HEMTs in Power Electronics

The use of WBG devices in Power Electronics starts from the need to overcome the limitations of Silicon devices, which have now reached their technological limit. Instead, WBG materials like Silicon Carbide (SiC) and GaN can be used in realizing devices with superior breakdown voltage, switching efficiency, lower on-resistance and smaller size thanks to their physical properties, as can be seen comparing the key material properties of Table 1.1 [7].

| Parameter                                | Si                | SiC                | GaN                |

|------------------------------------------|-------------------|--------------------|--------------------|

| Band Gap [eV]                            | 1.12              | 3.26               | 3.39               |

| Critical Field [MV/cm]                   | 0.23              | 2.2                | 3.3                |

| Electron Mobility [cm <sup>2</sup> /V·s] | 1400              | 950                | 1500               |

| Permittivity                             | 11.8              | 9.7                | 9                  |

| Thermal Conductivity [W/m·K]             | $15\cdot 10^{-3}$ | $38 \cdot 10^{-3}$ | $13 \cdot 10^{-3}$ |

Table 1.1 Key physical properties of Si, SiC and GaN.

The wider band gap energy of GaN results in a higher critical electric field and thus in a higher breakdown voltage, according to the approximated formula:

$$V_{BD} = \frac{1}{2} W_d E_c \tag{1.1}$$

where  $V_{BD}$  is the breakdown voltage,  $W_d$  is the drift region and  $E_c$  is the critical electric field. Hence, for the same breakdown voltage the drift region of a GaN device can be more than 10- and 1.5- times smaller than a Si or SiC one, respectively. This also leads to the reduction of the on-resistance  $r_{DS,on}$ , whose theoretical value for unit area can be expressed as:

$$r_{DS,on} = \frac{W_d}{q\mu_n N_D} \tag{1.2}$$

where q is the electron charge,  $\mu_n$  is the electron mobility and  $N_D$  is the total number of electrons in the region.

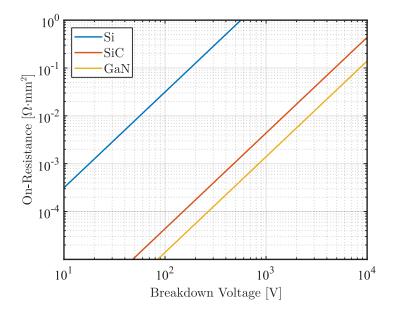

A straightforward indication of the performances of the power devices can be obtained expressing the theoretical on-resistance in relation to the breakdown voltage, according to:

$$r_{DS,on} = \frac{4V_{BD}^2}{\varepsilon_0 \varepsilon_r E_c^3} \tag{1.3}$$

which is obtained combining (1.1) with the Poisson's equation  $qN_D = \varepsilon_0 \varepsilon_r E_c/W_d$ , where  $\varepsilon_0$  is the vacuum dielectric constant. According to (1.3), it is possible to derive the ideal graph of Fig. 1.1 that compares the capability for Si-, SiC- and GaN-based power devices, showing how GaN HEMTs can theoretically achieve higher blocking voltages with a lower on-resistance.

Fig. 1.1 Theoretical curves of specific on-resistance vs. blocking voltage for Si, SiC and GaN technology

#### 1.4.1 Basic structures

One of the most important feature of the GaN HEMT derives from the chemical structure of GaN, called wurtzite, that is very chemically stable and mechanically robust, also confering to GaN some piezoelectric properties. When an AlGaN layer is made grown on the GaN crystal, a very high conductive region is formed at their interface, called two-dimensional electron gas (2DEG). The mechanisms leading to the formation of the 2DEG are mainly related to the spontaneous polarization, caused by the intrinsic asymmetry of the chemical bonds in the hexagonal wurtzite structure at the AlGaN-GaN interface, and to the piezoelectric polarization, that is caused by the mechanical compression of AlGaN on the GaN layer and generates an electric field. Therefore, a spontaneous layer with conductive electrons exists at the AlGaN-GaN interface and the confinement of the electrons in this very thin region increases their mobility up to 1500-2000 cm²/V·s.

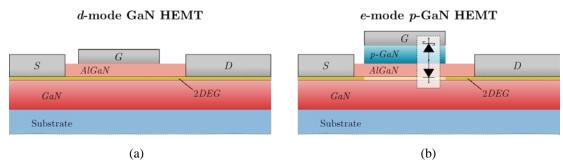

The spontaneous formation of the 2DEG causes the GaN transistor to be intrinsically a *normally-on* device, with the possibility to interrupt the current flow between source and drain contacts applying a negative gate voltage respect source and drain, realizing a depletion-mode (d-mode) transistor, as shown in Fig. 1.2 (a). However, in power electronics applications, it is desirable to work with normally-off devices in order to avoid undesired Short Circuit at the start-up of converters, simplify the control logic and ensure safety. For this reason, many technological solutions have been used to make *normally-off* GaN transistors, with the basic concept to create a potential barrier at the AlGaN-GaN

Fig. 1.2 Basic structures of the GaN HEMT: (a) depletion-mode GaN HEMT: the 2DEG is spontaneously formed at the AlGaN-GaN interface; (b) enhancement-mode p-GaN HEMT: the presence of a Schottky barrier inhibits the spontaneous formation of the conductive channel.

interface. This barrier can be lowered controlling the gate voltage to form the conductive channel between source and drain, to realize in such a way an enhancement-mode (e-mode) transistor. The most common solutions used to achieve this goal are [42]-[45]:

- recessed gate

- implanted gate

- p-doped GaN gate

- cascode configuration

Among these, the most common solution is the p-doped GaN gate, which consists in placing a positively charged GaN layer between the AlGaN and the gate metal contact. There are two types of gate contacts: ohmic and Schottky. The ohmic contact is typically used for low-power applications, where the gate voltage is small and the gate leakage current is not a significant issue, while Schottky contacts are typically used in high-power applications where a large gate voltage is required, providing better thermal stability but suffering of higher gate leakage current.

When the Schottky junction is formed underneath the gate, a potential barrier to the spontaneous formation of the 2DEG is created, realizing a normally-off device. The simplified structure of the Schottky-type p-GaN HEMT is shown in Fig. 1.2 (b). Because of the presence of the metal – p-GaN interface and the p-GaN – AlGaN – GaN interface, two back-to-back diodes are formed at the gate, as highlighted in Fig. 1.2 (b) [46].

#### 1.4.2 Electrical characteristics

The e-mode p-GaN HEMT can be turned-on, as a MOSFET, with a positive Gate-to-Source voltage  $V_{GS}$  exceeding the threshold voltage  $V_{GS,th}$ , that is normally in the range 0.7-2 V. On the contrary, it can be fully turned-off with zero  $V_{GS}$ , giving also the

possibility to avoid providing another supply voltage level on the driver circuit, even if this exposes the GaN HEMT to be more sensitive to voltage spikes on the Gate, demanding a particular attention to the layout design. Driving the Gate with a negative voltage is still feasible, but it increases the reverse conduction losses. In fact, even if there is not a body diode like in MOSFETs, the reverse conduction is still possible in GaN HEMTs thanks to their symmetric structure. As the 2DEG channel can be formed when  $V_{GS} > V_{GS,th}$ , the same can happen when the Gate-to-Drain voltage  $V_{GD}$  exceeds its

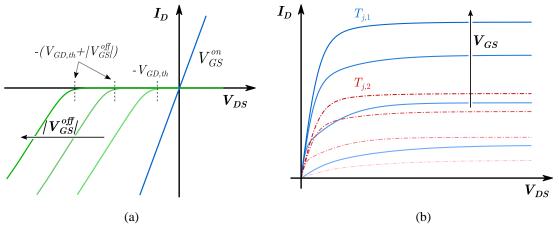

Fig. 1.3 Qualitative Reverse (a) and Forward (b) conduction characteristics of the e-mode GaN HEMT. The reverse conduction is characterized by a voltage drop at least equal to  $V_{GD,th}$ , to which the value of  $V_{GS}$  is added if a negative voltage is used to turn-off the device. In the Forward conduction, the increase of temperature from  $T_{j,1}$  to  $T_{j,2}$  causes the increase of the  $r_{DS,on}$  and the reduction of the saturation current.

relative threshold  $V_{GD,th}$ . However, the reverse conduction is characterized by a higher voltage drop than the diode forward voltage of the MOSFET, in the range of 3 – 5 V. This voltage drop is given by the quantity  $(V_{GD,th} - V_{GS}^{off})$ , which therefore increases if the HEMT is turned off with a negative  $V_{GS} = V_{GS}^{off}$ , causing excessive conduction losses.

However, since the reverse conduction behavior is not linked to the presence of a body diode, there is no reverse recovery and the related losses are then zero [7], [47]. The qualitative ideal reverse conduction characteristics for the GaN HEMT are shown in Fig. 1.3 (a).

Focusing on the output characteristics, during the forward conduction two regions can be observed:

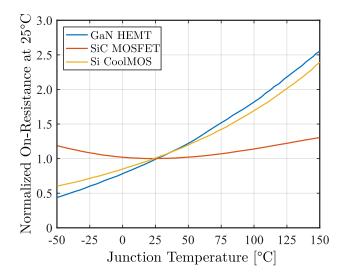

Fig. 1.4 Comparison of normalized  $r_{DS,on}$  in function of the junction temperature for three different 650 V power devices: GaN HEMT GS66516T by GaN Systems, SiC MOSFET IMZA65R027M1H by Infineon and Si CoolMOS IPW65R019C7 by Infineon. The variation of  $r_{DS,on}$  is larger for GaN and Si transistors than the SiC MOSFET.

- 1. A *linear region*, where the GaN HEMT behaves like a variable resistance, defined by the  $r_{DS,on}$  that is dependent on the  $V_{GS}$ , the junction temperature  $T_j$  and the Drain current  $I_D$ .

- 2. A saturation region, where the GaN HEMT behaves like a controlled current source, dependent on  $V_{GS}$ ,  $V_{DS}$  and  $T_j$ .

As  $T_j$  increases, the  $r_{DS,on}$  also increases and the  $I_D - V_{DS}$  curves are downshifted towards lower values of Drain current. The qualitative output curves of the GaN HEMT are depicted in Fig. 1.3 (b) at the varying of  $V_{GS}$  and for two junction temperatures, namely  $T_{j,1}$  and  $T_{j,2}$ , with  $T_{j,2} > T_{j,1}$ .

In general, the temperature variation of the  $r_{DS,on}$  is larger in GaN HEMTs than in SiC MOSFETs, due to the weaker thermal properties of GaN. For example, Fig. 1.4 compares the variation of  $r_{DS,on}$  with junction temperature from the nominal value at 25 °C for three power devices of different technology but with the same rated voltage of 650 V and very similar current ratings: a 59 A SiC MOSFET [48], a 75 A Si CoolMOS [49] and a 60 A GaN HEMT [50]. It is evident from the figure how the on-resistance of the GaN HEMT and the CoolMOS undergoes a greater variation, up to 2.5 times the nominal value at 150 °C, while the  $r_{DS,on}$  of the SiC MOSFET remains quite close to its rated value and is about 40% greater at 150 °C. This issue is mainly related to the weaker thermal properties

of GaN with respect SiC and prevents the use of GaN HEMTs in applications requiring high temperature operations, since the main advantages of GaN technology would be lost. So, especially for GaN HEMTs, it is crucial to adequately dissipate the heat generated during the operation in switching converters to keep  $T_j$  as low as possible in order to preserve the performances of the device.

#### 1.4.3 Capacitance and charge

One of the greatest advantages of the GaN HEMT consists in the very low value of its capacitances, determining excellent switching performances of the device. Last generation MOSFETs are optimized to reach switching frequencies up to few hundreds of kHz [51] thanks to the reduction of the semiconductor area and, as a consequence, of the parasitic capacitances at the expense of a higher on-resistance, since the first are inversely proportional and the second are directly proportional to the semiconductor area. GaN HEMTs can operate up to the MHz range maintaining a low on-resistance thanks to their superior physical properties. The value of the capacitances strongly depends on the area between the source, drain and gate contacts and since for GaN HEMTs this is much smaller than for MOSFETs, lower values are obtained.

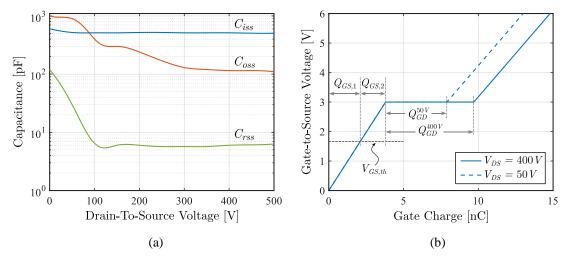

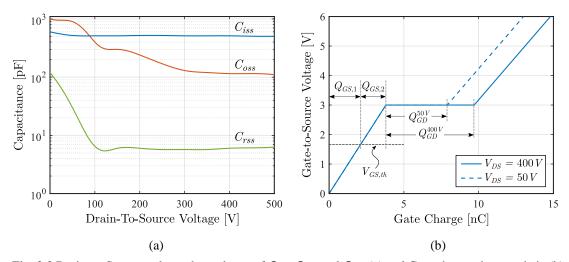

The capacitance determines the amount of charge needed to change the voltage between two terminals of the device, so lower capacitance leads to lower charge and a faster transition from one voltage level to another during the switching cycle. As in the MOSFET, three capacitances can be defined: the gate-to-source capacitance  $C_{GS}$ , the gate-to-drain capacitance  $C_{GD}$  and the drain-to-source capacitance  $C_{DS}$ . Looking into the gate with drain and source contacts shorted, the input capacitance is defined as  $C_{iss} = C_{GS} + C_{GD}$  and in the same way, when gate and source are shorted, the output capacitance can be defined as  $C_{oss} = C_{DS} + C_{GD}$ .  $C_{GD}$  is commonly called transfer or Miller capacitance and indicated as  $C_{rss}$ . While  $C_{iss}$  is weakly dependent on the  $V_{DS}$ ,  $C_{oss}$  and  $C_{rss}$  are a non-linear function of  $V_{DS}$  and can notably vary with it, as can be seen from Fig. 1.5 (a) that shows the input, output and reverse capacitances of the 650 V GaN HEMT GS66516T by GaN Systems [50].

The fast turn-on and turn-off switching transients of the GaN HEMT are achievable thanks to the very low amount of charge required by the input capacitance to switch the voltage across it. The dependence of the gate charge  $Q_G$  with the gate voltage  $V_{GS}$  is non-linear and its relationship for the 650 V GaN HEMT GS66516T is depicted in Fig. 1.5 (b). The total gate charge needed to drive the HEMT can be divided into different contributions, as highlighted in Fig. 1.5 (b), in which:

Fig. 1.5 Drain-to-source voltage dependence of  $C_{iss}$ ,  $C_{oss}$  and  $C_{rss}$  (a) and gate charge characteristic (b) of 650 V GaN HEMT GS66516T by GaN Systems.

- $Q_{GS}$  is the charge required to increase the voltage from zero to the plateau and can be defined as  $Q_{GS} = Q_{GS,1} + Q_{GS,2}$ , where  $Q_{GS,1}$  and  $Q_{GS,2}$  represent the charge required to increase  $V_{GS}$  up to the threshold voltage and from the threshold voltage to the plateau level, respectively.

- $Q_{GD}$ , also called Miller charge, is the charge required to commutate the HEMT's drain voltage and to enter the linear region of the  $I_D V_{DS}$  characteristic.  $Q_{GD}$  varies with the  $V_{DS}$  and its value can be obtained as

$$Q_{GD}(V_{DS}) = \int_{0}^{V_{DS}} C_{rss}(v) dv$$

(1.4)

where  $V_{DS}$  is the voltage to be commutated.

• After providing the amount of charge  $Q_{GS} + Q_{GD}$ , a further increase is required to reach the desired gate voltage: as it can be seen from Fig. 1.5 (b), if  $V_{GS} = 5$  V is the desired voltage, the total charge that must be provided is about 13 nC for  $V_{DS} = 400$  V.

GaN HEMTs enable very high frequency operations, so the voltage and current waveforms can be characterized by high dv/dt and di/dt during the switching cycle. When using Half Bridge-based topologies the high dv/dt at the switching node may cause the false turn-on of the off-state device, since during the voltage transition the current can flow in its  $C_{GS}$ , that is connected to the drain through the Miller capacitance  $C_{GD}$ . In many

cases this fact causes shoot-through, noise and additional power dissipation and eventually it can lead to the Short Circuit of the Half Bridge [52], [53]. One of the key parameters that should be considered to prevent this undesired issue is the Miller ratio, defined as the ratio  $Q_{GD}/Q_{GS,1}$ . The safe operation of the GaN HEMT is ensured and the false turn-on can be avoided if the Miller ratio is less than unity in all the operating conditions [7].

The output capacitance  $C_{oss}$  plays an important role in determining the switching behavior of the HEMT, since it is involved in the energy exchange with the other passive components of the circuit. To avoid hard-switching losses, Zero Voltage Switching (ZVS) is commonly used in power converters, exploiting the presence of an inductive current to discharge the output capacitances of the GaN HEMTs during the deadtime before turning them on. The ZVS behavior of the power device is strongly influenced by  $C_{oss}$ , since the necessary condition to achieve ZVS is expressed by [54]:

$$\frac{1}{2}LI^2 \ge Q_{oss}(V_{DC}) \cdot V_{DC} \tag{1.5}$$

where L is the inductor providing the current I in the bridge,  $V_{DC}$  is the bus voltage and  $Q_{oss}$  is the charge stored in  $C_{oss}$ , that depends on  $V_{DC}$ . As previously mentioned,  $C_{oss}$  is a non-linear function of  $V_{DS}$ , but it is possible to define a charge-equivalent linear capacitance  $C_{oss,Q}$  that provides the same value of  $Q_{oss}$  for each  $V_{DS}$  as:

$$C_{oss,Q} = \frac{\int_0^{V_{DS}} C_{oss}(v) dv}{V_{DS}} = \frac{Q_{oss}(V_{DS})}{V_{DS}}$$

(1.6)

Combining (1.5) and (1.6), with  $V_{DS} = V_{DC}$ , the ZVS condition can be expressed as:

$$\frac{1}{2}LI^2 \ge C_{oss,Q}(V_{DC}) \cdot V_{DC}^2 \tag{1.7}$$

If the condition found in (1.7) is not fulfilled, incomplete soft-switching occurs on the device that is turning on causing high power dissipation, since its  $C_{oss}$  is not fully discharged.

#### 1.4.4 Figure of Merit

It is convenient to use a unique parameter to evaluate and compare the performances of power transistors to take the best choice for an application. The Figure of Merit (FOM) permits to compare the key features of transistors of different technologies according to the minimum hard-switching losses achievable for each technology. Many ways to define

the FOM have been proposed in the literature [55]-[59], starting from the computation of the minimum possible power dissipation during the switching cycle.

The power dissipated in a switch can be divided into two components: the conduction losses and the switching losses. The first represents the power dissipated on the onresistance during the conduction interval of the switch and is equal to  $r_{DS,on}I^2$ . The second term is dependent on the switching frequency, the voltage and current to be commutated, the output capacitance, the reverse recovery and the reverse conduction. It becomes quite difficult to consider all these parameters when computing the total power loss and the FOM, but it is necessary to perform a coherent evaluation on the performances of the power device.

One of the most complete FOM formulation, named Hard-Switching-FOM (HSFOM), is proposed in [59] and is defined as:

$$HSFOM = \frac{1}{\sqrt{r_{DS,on}Q_{oss}} + k\tau_{rr}\sqrt{f_{sw}V_{sw}}}$$

(1.8)

in which  $f_{sw}$  is the switching frequency,  $V_{sw}$  is the voltage that must be commutated,  $\tau_{rr}$  is the reverse-recovery time and k is a parameter dependent on the topology of the converter considered for the FOM computation. The HSFOM takes into account all the power loss contributions described above, but it requires a great effort for its computation and moreover is topology-dependent.

GaN HEMTs do not have the body diode, so the reverse-recovery time and the related losses are zero. This leads to the simplification of (1.8) when computing the FOM for GaN devices, that becomes:

$$HSFOM = \frac{1}{\sqrt{r_{DS.on}Q_{oss}}}. (1.9)$$

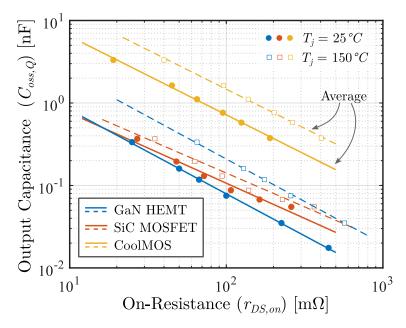

In this case, a useful FOM definition can be found in [55], where the key parameters used to determine the performances of the device are  $r_{DS,on}$  and  $C_{oss,Q}$ , that only depend on the device properties and, for this reason, this FOM is also named Device-FOM (DFOM). It is defined as:

$$DFOM = \frac{1}{\sqrt{r_{DS,on}C_{oss,Q}}}. (1.10)$$

Moreover, the DFOM is independent from the semiconductor area  $A_{semi}$ , since  $r_{DS,on}$  is proportional to  $1/A_{semi}$  and  $C_{oss,Q}$  is proportional to  $A_{semi}$ .

A comparative analysis of  $r_{DS,on}$  and  $C_{oss,Q}$  has been performed in this section considering three power devices families of different technologies with 650 V breakdown voltage: GaN HEMTs by GaN Systems, SiC MOSFETs and Si CoolMOS transistors by Infineon. Six devices for each family have been considered and the  $r_{DS,on} - C_{oss,Q}$  values have been extracted from the datasheets at  $V_{DS} = 400$  V and two junction temperatures, 25 °C and 150 °C, and they are plotted in Fig. 1.6. The circles and the squares represent the single power devices at 25 °C and 150 °C, respectively, while the lines show the linear regression of the computed values and are used to compare the performances of the different technologies, since they are directly related to the DFOM, representing the points at which the product  $r_{DS,on}C_{oss,Q}$  is constant. Lower lines in the graph indicate better performances of the device, so it is evident how WBG devices outperform Si MOSFETs and, in particular, GaN HEMTs show the best FOM at 25 °C.

However, at  $T_j = 150$  °C GaN HEMTs experience a greater increase of  $r_{DS,on}$  than SiC MOSFETs, which therefore still represent the most suited technology for high-temperature operations. However, even if the DFOM provides fast and meaningful results in first analysis, for a correct and complete comparison with GaN HEMTs, the contribution of the reverse-recovery time and the switching frequency should be considered in the computation of the FOM for SiC MOSFETs and (1.8) should be used.

Fig. 1.6 Figure of Merit for different technologies of 650 V power devices: GaN HEMT by GaN Systems, SiC MOSFET and Si CoolMOS by Infineon. WBG technology greatly outperforms Si-based technology. GaN HEMTs show the best FOM at  $T_j = 25$  °C but their performances deteriorate at  $T_i = 150$  °C, where SiC MOSFET still represent the best solution.

#### 1.4.5 Modeling of GaN HEMTs

The modeling of power devices is often a complex process and requires a great effort to achieve a highly accurate and time-saving solution. At the same time it is necessary to have a reliable model of the real power device, since it could be used to perform simulations and power losses analysis, and also to provide an useful instrument to understand and improve the technology of power devices. Depending on the final goal and the application field, numerous modeling approaches have been proposed [60], listed here in order of increasing accuracy and complexity:

- behavioral models

- semi-physical models

- physics-based models

- semi-numerical models

- numerical models.

Behavioral models are computed starting from the experimental tests on the device and deriving a function that describes its behavior through the fitting of many parameters, that have no direct physical meaning. These model, though the simplest ones in terms of time and computational complexity, are the less accurate since neglect many real aspects of the device that can take place during its operation. Moreover, they are quite dependent on the condition at which are computed, so a change in the operating condition may cause loss of accuracy.

Semi-physical models take some advantages from both behavioral and physics-based models. The equations describing the behavior of the device are derived from physics and adapted through the fitting of some parameters. These model are normally used in simulation environments such as SPICE and are mainly intended to application-level simulations, e.g. to analyze power converter topologies or evaluate power losses and efficiency with an acceptable level of accuracy.

Physics-based models are based on the physical phenomena involved in the semiconductor device and are derived solving the related physical equations. This requires the knowledge of semiconductor physics, as well as a big effort in writing and solving the analytical equations, and therefore they are intended for device-level simulations.

Semi-numerical and numerical models are based on the knowledge of semiconductor physics, device geometry and material properties. The physical equations are then solved through numerical methods like Finite Element Analysis. These numerical models are used by software such as Sentaurus, TCAD and SILVACO and are the most complex and

accurate, providing an important tool to analyze power semiconductor and improve their technology.

The models of GaN HEMTs presented in the literature are for the majority behavioral and physical ones and many of them were developed for the d-mode GaN HEMTs and then adjusted for e-mode HEMTs [61]-[66]. Recently, two physics-based models became industry-standard for the compact modeling of radio-frequency and high voltage GaN HEMTs: the Massachusetts Institute of Technology (MIT) virtual source GaN HEMT model (MVSG) [67] and the advanced SPICE model (ASM) [68], [69]. In this last one, the classic SPICE semi-physical approach is replaced by an accurate numerical model, which includes also nonlinear phenomena, such as the charge trapping. The charge trapping mechanism attracted a lot of interest from the modeling perspective, since it strongly impacts the dynamic response and the performances of GaN HEMTs. Therefore, many physical approaches have also been introduced in the literature to model the charge trapping [64], [69]-[72].

With the increasing development of Artificial Intelligence (AI), some behavioral models based on Artificial Neural Networks (ANN) have also been proposed in the last years, showing good adaptability to GaN HEMTs of different manufacturers [73], [74].

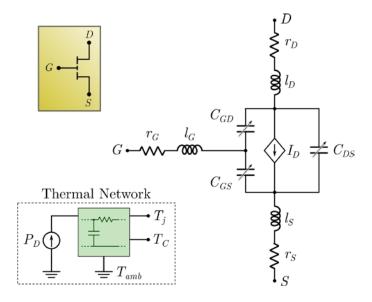

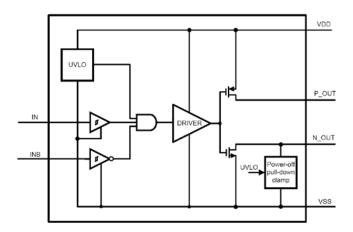

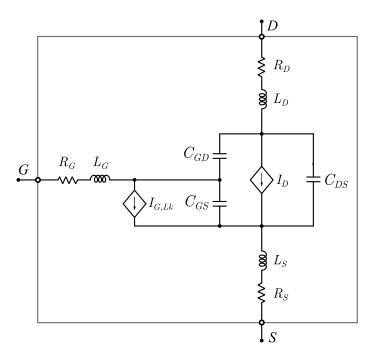

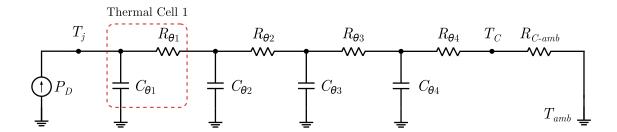

The GaN HEMTs' manufacturers usually provide a SPICE model of their devices, as is the case of Infineon, EPC and GaN Systems [75], [76]. These models are based on the experimental characterization of the transistors led by the manufacturers and are intended for the simulation of the GaN HEMTs in power converters, guaranteeing good accuracy and low computation time. In general, they consist of an electro-thermal network that includes both the main electrical and thermal relations of the device, as shown in Fig. 1.7. The model contains the parasitic resistances and inductances at gate (G), drain (D) and source (S) contacts, while the capacitances  $C_{GS}$ ,  $C_{GD}$  and  $C_{DS}$  are modeled as variable charge sources dependent on the voltages  $V_{GS}$ ,  $V_{GD}$  and  $V_{DS}$ . The drain current  $I_D$  is represented by a controlled current source, dependent on  $V_{GS}$ ,  $V_{DS}$  and  $T_j$  and it is used to compute the instantaneous power dissipation  $P_D = V_{DS}I_D$ , that is the input for the thermal network along with the ambient temperature  $T_{amb}$ . The thermal network is generally modeled according to the Cauer thermal model, consisting of different cascaded RC cells, corresponding to an equivalent representation of the measured thermal resistances and capacitances between junction and case.

Depending on the desired level of accuracy, various simplifications can be made in the model, such as neglecting the thermal model or the presence of parasitic inductances. However, since the performance of the GaN HEMT is highly dependent on the temperature, neglecting the thermal model would lead to unrealistic results or incorrect analysis.

Fig. 1.7 General equivalent model for SPICE provided by GaN HEMTs' manufacturers.

As an example, the SPICE model of the 650 V - 60 A GaN HEMT by GaN Systems, available in [50], provides two levels of accuracy. The complete model, including the thermal network, will be briefly presented here, as it will be the starting point of the discussion led in Chapter 4.

All the parameters used in the model are listed in Table 1.2. The drain current of the device for  $V_{DS} > 0$  and  $V_{DS} < 0$  is expressed by equations (1.11) and (1.12), respectively:

$$I_D = c \left[ a_1 - a_2 (T_j - T_0) \right] \cdot ln \left( 1 + e^{k(V_{GS} - V_{th})} \right) \cdot \frac{V_{DS}}{1 + f(V_{GS}) \cdot V_{DS}}$$

(1.11)

$$I_D = -c[a_1 - a_2(T_j - T_0)] \cdot ln(1 + e^{k(V_{GD} - V_{th})}) \cdot \frac{V_{SD}}{1 + f(V_{GD}) \cdot V_{SD}}$$

(1.12)

where the functions  $f(V_{GS})$  and  $f(V_{GD})$  are of the form  $f(v) = x_0 + x_1(v + x_2)$ . The temperature dependence of the on-resistance is modeled by two variable resistors placed in series to the  $I_D$  current source, one on the drain side and another on the source side. The equations for the model of these two variable resistances are:

$$r_D = I_D \cdot sh_d \cdot m_{res} \cdot \left(1 - r_{Tc} \cdot (T_j - T_0)\right) + gan_{res} \left(\frac{T_j + 273}{T_0 + 273}\right)^{g_{Tc}}$$

(1.13)

$$r_{S} = I_{D} \cdot sh_{S} \cdot m_{res} \cdot \left(1 - r_{Tc} \cdot (T_{j} - T_{0})\right) + gan_{res} \left(\frac{T_{j} + 273}{T_{0} + 273}\right)^{g_{Tc}}$$

(1.14)

The capacitances among G, S and D are modeled as a variable charge source in parallel to a constant capacitance. The basic form of the equations used for  $C_{DS}$  and  $C_{GD}$  is:

$$Q(v) = \sum_{j=1}^{4} \alpha_{1j} \cdot \ln\left(1 + e^{\alpha_{2j}(v + \alpha_{3j})}\right)$$

(1.15)

while the model of  $C_{GS}$  is expressed by:

$$Q(V_{GS}, V_{DS}) = \left(\sum_{j=1}^{4} \beta_{1j} \cdot \left(1 - \frac{1}{1 + e^{\beta_{2j}(-V_{DS} + \beta_{3j})}}\right) + \sum_{j=1}^{4} \gamma_{1j} \cdot \left(\frac{1}{1 + e^{\gamma_{2j}(-V_{DS} + \gamma_{3j})}} - 1\right)\right) \cdot V_{GS}$$

(1.16)

which has to incorporate the dependence with both  $V_{DS}$  and  $V_{GS}$ . The constant parameters  $\alpha_{ij}$ ,  $\beta_{ij}$  and  $\gamma_{ij}$  used in (1.15) and (1.16), with i = 1, ..., 3 and j = 1, ..., 4, can be found in [50] and are not reported here for brevity.

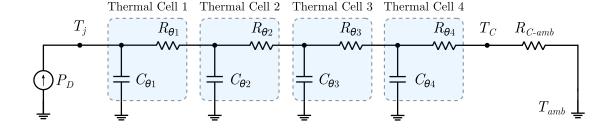

Finally, the equivalent thermal model is represented through four RC cells according to the Cauer model, as shown in Fig. 1.8, where the case-to-ambient thermal resistance  $R_{C-amb}$  is also considered. The parameters  $C_{\theta i}$  and  $R_{\theta i}$  are the thermal capacitance and resistance of each cell and they are listed in Table 1.3, along with their time constants.

Fig. 1.8 Thermal model for the GaN HEMT GS66516T by Gan Systems.

| Symbol              | Value | Unit                      |          |        |                           |  |

|---------------------|-------|---------------------------|----------|--------|---------------------------|--|

| $T_0$               | 25    | °C                        |          |        |                           |  |

| Drain Current Model |       |                           |          |        |                           |  |

| Symbol              | Value | Unit                      | Symbol   | Value  | Unit                      |  |

| С                   | 0.105 | A/V                       | $V_{th}$ | 1.61   | V                         |  |

| $a_1$               | 174.1 | -                         | $x_0$    | 1.1    | -                         |  |

| $a_2$               | 0.798 | $^{\circ}\mathrm{C}^{-1}$ | $x_1$    | 1.1    | $V^{-2}$                  |  |

| k                   | 26.0  | $V^{-1}$                  | $x_2$    | 1.0    | V                         |  |

| On-Resistance Model |       |                           |          |        |                           |  |

| Symbol              | Value | Unit                      | Symbol   | Value  | Unit                      |  |

| $sh_d$              | 0.943 | $A^{-1}$                  | $sh_s$   | 0.052  | $A^{-1}$                  |  |

| $m_{res}$           | 0.002 | Ω                         | $r_{Tc}$ | -0.004 | $^{\circ}\mathrm{C}^{-1}$ |  |

| $gan_{res}$         | 0.022 | Ω                         | $g_{Tc}$ | 2.85   | -                         |  |

Table 1.2 Parameters for drain current and on-resistance SPICE models of the GS66516T.

Table 1.3 Parameters for the thermal model of GS66516T.

| Thermal Model                  |                      |                                     |        |               |                      |  |

|--------------------------------|----------------------|-------------------------------------|--------|---------------|----------------------|--|

| Thermal Capacitance<br>[Ws/°C] |                      | rmal Capacitance Thermal Resistance |        | Time Constant |                      |  |

|                                |                      | [°C                                 | [°C/W] |               | [s]                  |  |

| Symbol                         | Value                | Symbol                              | Value  | Symbol        | Value                |  |

| $C_{\theta 1}$                 | $1.4 \cdot 10^{-4}$  | $R_{\theta 1}$                      | 0.01   | $	au_1$       | $1.40 \cdot 10^{-6}$ |  |

| $C_{	heta 2}$                  | $1.23 \cdot 10^{-3}$ | $R_{\theta 2}$                      | 0.14   | $	au_2$       | $172 \cdot 10^{-6}$  |  |

| $C_{	heta 3}$                  | $10.8 \cdot 10^{-3}$ | $R_{\theta 3}$                      | 0.14   | $	au_3$       | $1.5 \cdot 10^{-3}$  |  |

| $C_{	heta 4}$                  | $3.3 \cdot 10^{-3}$  | $R_{	heta 4}$                       | 0.01   | $	au_4$       | 33·10 <sup>-6</sup>  |  |

#### 1.4.6 Reliability aspects

The extreme potential and the limitations of GaN technology have been investigated in detail during the last years in different application fields, from radio-frequency to power electronics. Despite excellent features reported for GaN HEMTs, some issues still undermine their performances and reliability, such as dispersion, trapping and parasitic effects, as well as long-term stability [28], [77], [78].

Charge trapping can occur due to a variety of factors, including defects in the device structure, surface states, and interface traps. The presence of defects in the structure of the device causes deep levels that can be dynamically filled by holes and electrons depending on the device operating conditions, affecting the local potential and leading to possible instability. Moreover, the energy levels of the defects as well as their physical location

can lead to different issues, such as the variation of the DC operating point in power amplification, the drain current collapse and threshold voltage and on-resistance shifts [28], [77]-[79].

The current collapse consists in the drain current reduction and in a decrease in device performance. The main cause of current collapse is the trapping of electrons in surface states or defects in the AlGaN/GaN heterojunction, leading to the reduction in the effective channel conductivity. Different mechanisms for current collapse have been proposed, including trap-assisted tunneling and impact ionization, and several solutions have been introduced to mitigate this phenomenon, such as passivation techniques and gate-recessed structures [80].

Dynamic on-resistance is another critical aspect in GaN HEMTs, that causes an increase of the on-resistance during switching operation. High values of  $r_{DS,on}$  can lead to increased power dissipation and decreased efficiency. One of the main causes of dynamic- $r_{DS,on}$  is related to hot electrons, consisting in high-energy electrons that gain kinetic energy from the applied electric field. They are generated under high-voltage and high-frequency operation and cause degradation of the device, not only affecting the on-resistance, but also causing increased gate leakage and the threshold voltage shift. Several studies have proposed various mitigation techniques for hot electron degradation, such as using thicker barrier layers, improving the gate insulation, and reducing the electric field. In addition, the on-resistance increase is also temperature-dependent, further limiting the operation of GaN HEMTs at high voltages and temperatures, even if optimization on the structure and, in particular on the buffer layer, can suppress this effect [31], [81], [82].

Temperature is another relevant parameter that is responsible for degradation of GaN HEMTs, especially for high-power applications, where they can operate at high junction temperature for long time. The high temperature reverse bias (HTRB) stress is commonly used to evaluate the reliability of GaN HEMTs for high voltage operations. This condition can lead to permanent degradation of the on-state current and the transconductance and can also cause the threshold voltage shift and the gate leakage current increase [83], [84]. In addition to this permanent degradation, some positive effects have been reported like the decrease of gate leakage current and a decrease of current collapse during pulsed measurement during the HTRB test. The impact of temperature cycling on the reliability of GaN HEMTs was studied in [85], finding that thermal stress caused by repeated temperature changes led to device degradation and failure. The use of GaN HEMTs under extreme temperatures operation has been proved in [86], where a HEMT device with InAlN/GaN lattice matched configuration was fabricated allowing 1-MHz large-signal operation at 1000 °C in vacuum for 25 hours, without evidencing major degradation of the heterostructure.

The external influence of the environment on GaN HEMTs was also studied and particular attention was brought to radiation hardness to evaluate the use of GaN HEMTs in aerospace and military applications [87], [88]. Like all semiconductor devices, GaN HEMTs can be susceptible to damage from ionizing radiation. One of the main effects of radiation on GaN HEMTs is the creation of charge carriers, which can cause changes in device properties and potentially lead to device failure. In addition, radiation can also cause defects in the device structure, which can also impact device performance. Several studies have investigated the radiation hardness of GaN HEMTs, with varying results depending on the type and dosage of the used radiation. The charge carrier density has been identified to be relatively insensitive to gamma rays, that in low doses seem to bring even improvements in device performances, even if high doses of gamma rays can result in severe degradation [89]. Moreover, the impact of heavy-ion irradiation on GaN HEMTs exhibited significant degradation in performance at high radiation doses, but also showed their recovery capability after a long restoring period [90], [91].

#### 1.5 Short Circuit robustness of GaN HEMTs

One of the key aspects in power electronics is the robustness of power devices. In fact, the ability to bear high electro-thermal stress without experiencing catastrophic failures is a crucial point in power converters that must operate without interruption and with high levels of safety and reliability. With the increasing development of power electronics in the perspective of a more sustainable future and energy management, the need of highly reliable conversion systems spread to all the application fields, such as automotive, industry, military, data centers, servers, communication systems and renewables. In this context, the employment of robust and reliable power devices is mandatory [92]-[94].

In particular, the capability to handle Short Circuit (SC) conditions is a core aspect of the robustness of power device. The majority of power converters for the latter application fields is based on Half Bridge (HB) and Full Bridge (FB) configurations, such as 1-phase and 3-phase inverters, resonant DC/DC power converters, DAB and DAB-based topologies and so on. In all the converters based on HB or FB topology there is the risk to cause faults due to the SC of a bridge-leg, leading to the breakdown of the power devices and damages to the whole system. The SC fault can be caused by the power devices degradation, such as thermal runaway, gate rupture or aging, but also by auxiliary circuit malfunctions and poor layout design, that could make the devices susceptible of noise and false turn on.

Some solutions must be led in the design process to prevent and mitigate the SC failure in power converters, possibly without interrupting their operation. This is commonly achieved using fault-detection methods and realizing a protection against the fault event.

The fault-detection is dependent on the converter topology, as different solutions can be provided for inverters and multi-modular DC/DC converters [94]-[96]. The protection, instead, is often realized adding a protection circuit in the gate driver circuit of the power devices, using redundant devices or using auxiliary switches to change the configuration of the bridge and ensure the safe operation of the converter, even if with reduced performances. The hardware redundancy can be performed in different ways: on switch-level, using series or parallel redundant power devices; on leg-level, using redundant bridge legs in the converter; on module-level, in the case of modular converters; on system-level, using redundant series/parallel converters [94], [95].

In order to evaluate the impact of SC on the operation of the device and to design a protection circuit, SC capability tests are performed on the power devices to characterize the electro-thermal stress and the possible boundary conditions that prevent the devices from the catastrophic failure.

As Si MOSFETs and IGBTs have been the leading power devices in medium and high power applications for long years, the research widely focused on their SC robustness, contributing to the improvement of Si-based semiconductor technology, that has reached the highest levels of reliability. On that basis, the recent development of WBG semiconductors as valuable substitutes of Si devices to reach higher performances, efficiency and power density led to an extensive study of the SC behavior on SiC and GaN devices as well [33]-[41], [98]-[105].

Starting from the extensive literature on SC behavior of IGBTs, three types of SC events can be distinguished for a power device [97]:

- Short Circuit type I (SC-I) is the direct turn-on of the device while its  $V_{DS}$  is high. In this condition,  $V_{GS}$  is initially low with  $V_{DS}$  high, like in the normal offstate condition. While  $V_{DS}$  is still high, a positive  $V_{GS}$  is applied, turning on the device, that operates in its saturation region, causing a high peak drain current. This type of SC is also called Hard Switching Fault (HSF).

- Short Circuit type II (SC-II) is the occurrence of the SC during the on-state of the device. In this case, before the SC event the device is conducting the load current and its  $V_{DS}$  assumes the on-state value, close to zero. When the SC occurs,  $V_{DS}$  becomes equal to the DC-link voltage and the current suddenly increases with a di/dt defined by the DC-link voltage and the parasitic inductance in the circuit. This type of SC is also defined as Fault Under Load

- (FUL) and it can be more dangerous for the device, as higher current peak and power dissipation are involved.

- Short Circuit type III (SC-III) occurs when the SC happens on the load path during the switching of the leg, involving the anti-parallel diodes of the devices that are turning on. This condition is quite similar to SC-II, involving a high current peak, but before the SC event the current flows in the diode and the reverse recovery contributes to the increased current peak. For GaN HEMTs, where no body diode and the related reverse recovery is present in the structure, this condition can be assumed to be close to SC-II event.

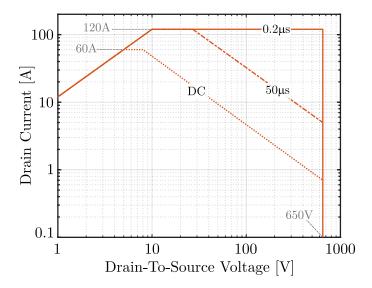

Many different studies on the Short Circuit (SC) robustness of GaN HEMTs have been performed in recent years. As the most suitable for high power and voltage applications, GaN HEMTs with a breakdown voltage higher than 600 V have been commonly tested. All the experimental SC tests are led focusing on the HSF, where a single device under test (DUT) is characterized in terms of withstand time, energy, time to failure, degradation, instability and failure mechanisms [33]-[41], [105]. In many cases, a device with higher current rating is placed in series to the DUT to protect the circuit in case of failure of the DUT, which could lead to damage to other components on the board.

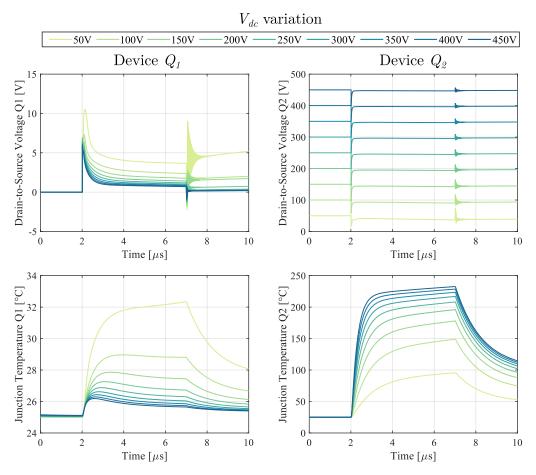

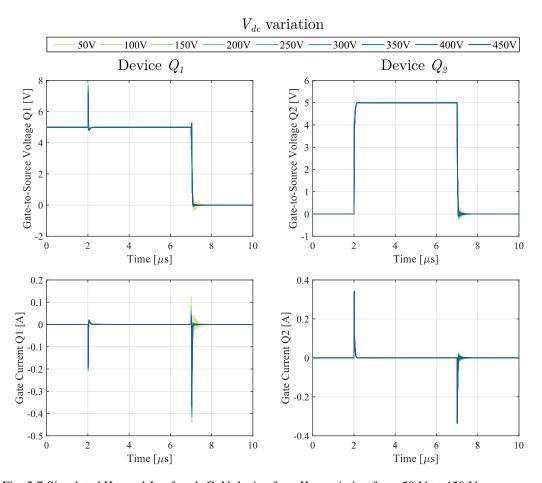

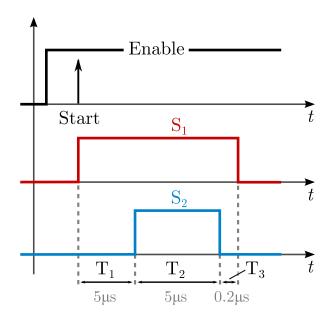

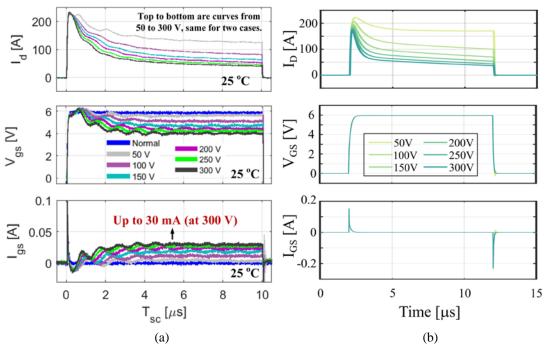

The robustness of a 650 V – 60 A GaN HEMT under various SC conditions is studied in [34]. In particular, the effects of the DC-link voltage  $V_{dc}$ , gate-to-source voltage  $V_{GS}$ , temperature and type of SC event are discussed. Two types of SC tests are investigated: a single event SC, with a fixed 10  $\mu$ s pulse-width, and repetitive SC events, with SC pulse-width increased with 200 ns steps up to the failure of the DUT.

The single event SC tests provides information about the capability of the device. In this type of tests, when  $V_{GS}=6$  V, the recommended driving condition for this device, the DUT showed a good capability for  $V_{dc}$  lower than 350 V, surviving all the SC events, both at 25 °C and 125 °C. However, for  $V_{dc} \ge 350$  V the DUT fails in less than 700 ns, highlighting a critical aspect of the device. The destruction of the device is attributed to the extreme rise of temperature in a small region of the device, that leads to the melting of the contacts, caused by the high current density. Gate-drain insulation also failed, as  $V_{GS}$  overcame its maximum voltage limit. The failure of the device can be avoided for  $V_{dc}$  up to 450 V if a reduced gate driving voltage is used, as demonstrated in the work.

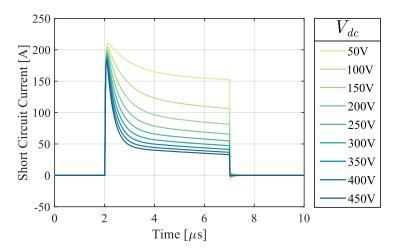

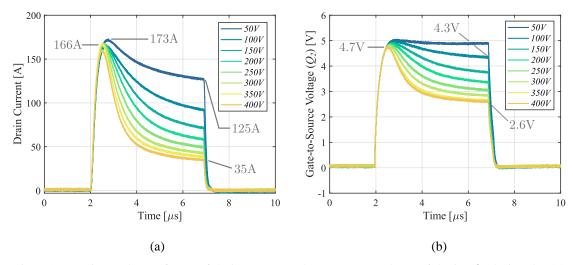

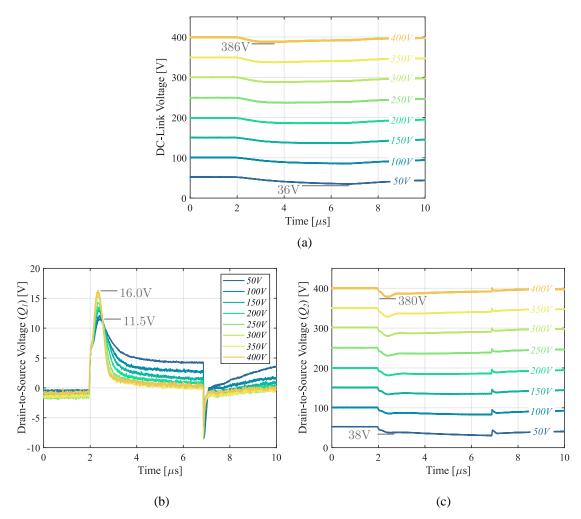

The main features of the SC behavior of the DUT are also discussed. In particular, the strong negative temperature feedback of device conductivity, caused by the reduction of the carrier mobility and the channel temperature increase, acts as a self-regulation for the drain current. At the beginning of the SC event, the peak drain current is dependent on  $V_{GS}$  and it reaches about 240 A at 6 V. During the SC, the drain current experiences a dramatic reduction, that depends on the dissipated power and, so, on the applied  $V_{dc}$ . At

50 V, the final value of the current is about 120 A, while at 300 V it decays to 40 A. The increment of the test temperature is beneficial for the reduction of the current, that is even lower at the end of the SC, because  $T_i$  is higher.

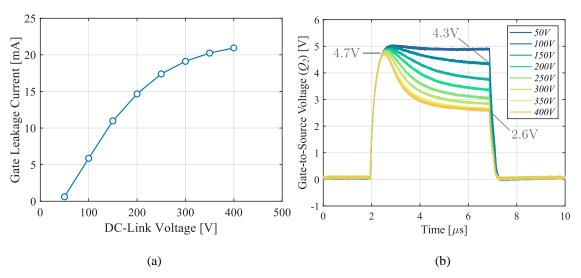

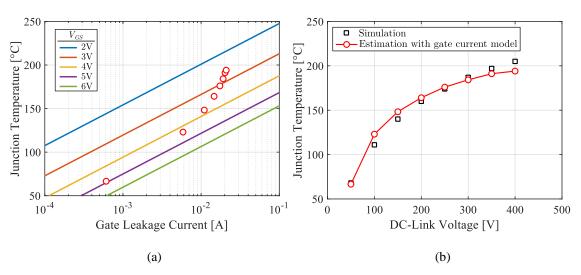

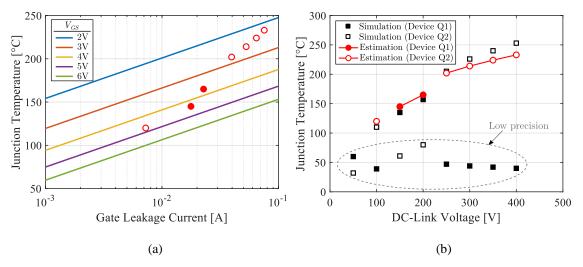

Another mechanism found to be relevant for the SC event consists in the gate leakage current increase. In nominal conditions ( $V_{GS} = 6 \text{ V}$ ,  $T_j = 25 \,^{\circ}\text{C}$ ), its value is 300  $\mu\text{A}$ , but during the SC event it is increased up to 30 mA, due to the increase of  $T_j$ . This phenomenon results in the reduction of  $V_{GS}$  applied to the DUT, since a larger voltage drop occurs on the external gate resistor. This fact is considered to be a further beneficial mechanism that helps in reducing the drain current during the SC event.

Then, the authors compute the energy involved during the non-destructive SC tests and define the critical energy that caused the failure of the device. For  $V_{dc}$  between 300 V and 400 V the SC energy is between 150 mJ and 220 mJ.

The repetitive SC tests are used to evaluate the degradation of the DUT and the maximum subsequent SC cycles that it can survive. Two scenarios have been investigated: first, repetitive SC event with increasing SC pulse-width at fixed  $V_{dc} = 300 \text{ V}$ ; second, repetitive tests with fixed SC pulse-width and fixed low voltage  $V_{dc} = 20 \text{ V}$ . Both the scenarios led to degradation of the device, observable in the I – V curves, the drain leakage current, the gate leakage current and the threshold voltage. In the first case, the DUT fails after seven pulses and show the reduction of the gate leakage currents and of the threshold voltage, and a slight reduction of drain leakage current for  $V_{DS} > 300 \text{ V}$ . In the second condition, the DUT can survive more than 100 SC pulses, but it shows a severe degradation of I – V curves, along with the reduction of drain leakage current and the increase of the threshold voltage.

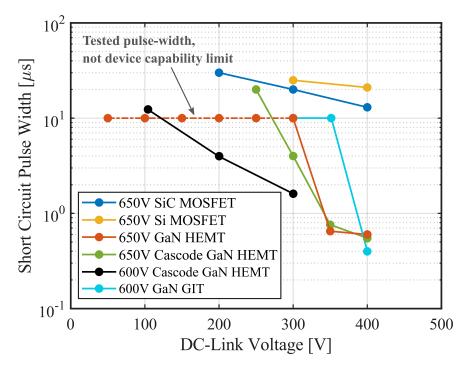

Some critical aspects of the 650 V – 60 A GaN HEMT are pointed out in this work, as the reduced SC capability for high  $V_{dc}$  values that are commonly adopted for the DC-link when using 650 V-devices and the reduced capability to survive repetitive SC tests. The first aspect is critical in comparison to Si and SiC technologies, that show a higher SC robustness, with a withstand time greater than 10  $\mu$ s at  $V_{dc} = 400$  V, while it is less than 700 ns for the DUT. However this issue is not related to the specific tested DUT, as also other families of GaN devices with the same voltage ratings show weak SC robustness at high voltages. For instance, the SC withstand times of different 600- and 650-V power devices are compared in Fig. 1.9. Si and SiC MOSFETs have the highest SC capability, while all devices based on GaN technology show clear worse performances at high voltages in terms of SC robustness. This fact is related to the deep difference in the physical structure of GaN-based transistors, that are lateral devices, and is a limiting factor for the spread of GaN HEMTs in all power electronics applications.

Fig. 1.9 Short Circuit withstand time of different 600/650 V power transistors [34].

The SC capability of others GaN HEMTs are evaluated in the literature. In [33], the DUT is a 650 V – 15 A device, tested both for single and repetitive SC events with an IGBT as a protection on the DC-link. In the test conditions  $V_{dc} = 400 \text{ V}$ ,  $V_{GS} = 6 \text{ V}$  the device shows a long SC withstand time, more than 600  $\mu$ s, at the opposite of the 60 A device. The same explanations are given about the drain current self-regulation mechanism and the long withstand time is attributed to the dramatic drop of the current, that in turns slows down the rise of  $T_j$ . For repetitive SC tests, however, the DUT exhibits a withstand time lower than 1  $\mu$ s in the same conditions and fails at the second pulse.

To evaluate the sensitivity of the DUT to the operating conditions,  $V_{GS}$ ,  $V_{dc}$  and the SC pulse-width  $t_{SC}$  were varied. The reduction of  $t_{SC}$  from 1  $\mu$ s to 45 ns leads to a higher withstand time in repetitive tests and the device fails at the 13<sup>th</sup> SC event. However, the reduction of  $V_{dc}$  and  $V_{GS}$  has a greater impact on SC behavior than  $t_{SC}$ . In fact, with  $V_{dc} = 200$  V no failure of the DUT happens after 4000 cycles with  $t_{SC} = 1$   $\mu$ s, while the reduction of  $V_{GS}$  from 6 V to 3 V implies no failure up to 2000 cycles.

The impact of dynamic  $V_{GS}$  on the SC behavior is also evaluated by turning on the DUT before applying the whole  $V_{dc}$  across it. The results showed a clear dependence on the time duration between the turn-on of the DUT and the SC event, with a reduction of the peak drain current with the increase of this duration.

Simulation analysis is also provided to investigate the failure mechanism of the DUT, showing the temperature distribution along the device during the SC and highlighting the extreme temperature increase in the gate-drain region. The analysis of the failure spot on a decapsulated failed device is performed through a focus ion beam cutting, showing that the high rise of temperature can lead to the formation of cracks at the interface between the GaN buffer layer and the transition layers, that can be even propagated to the other parts of the device.

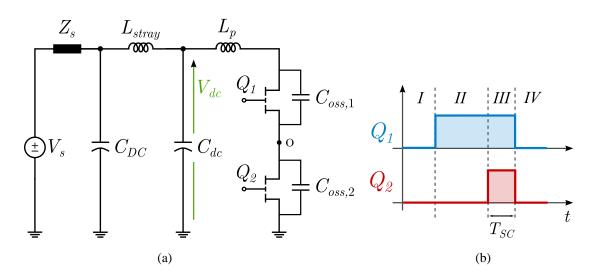

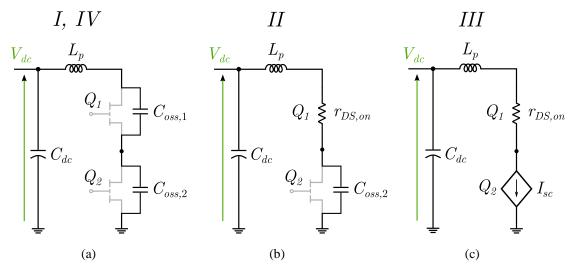

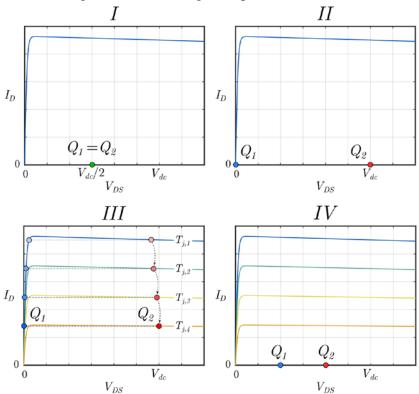

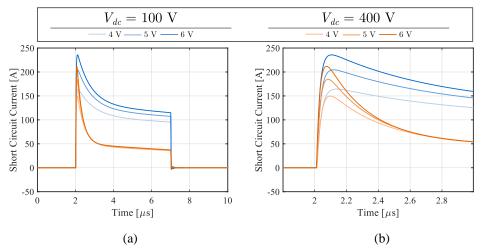

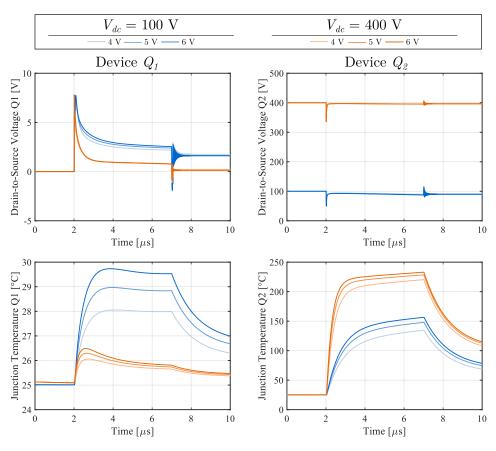

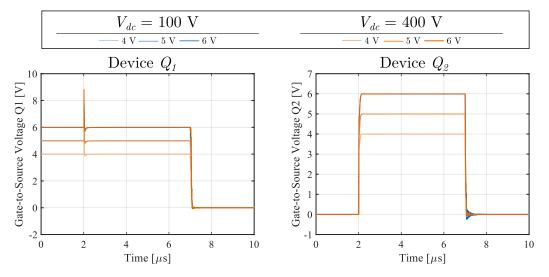

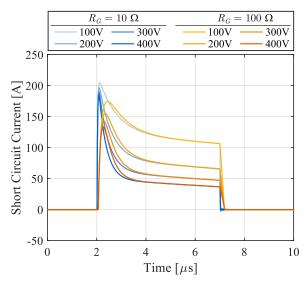

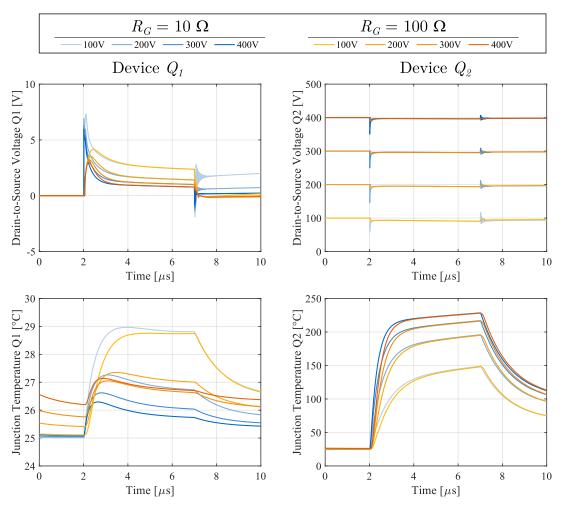

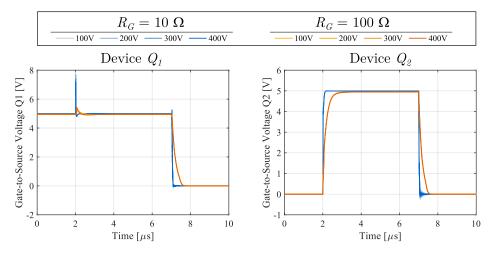

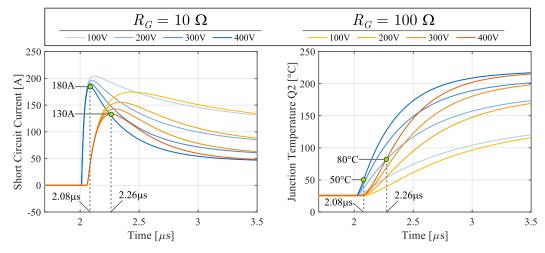

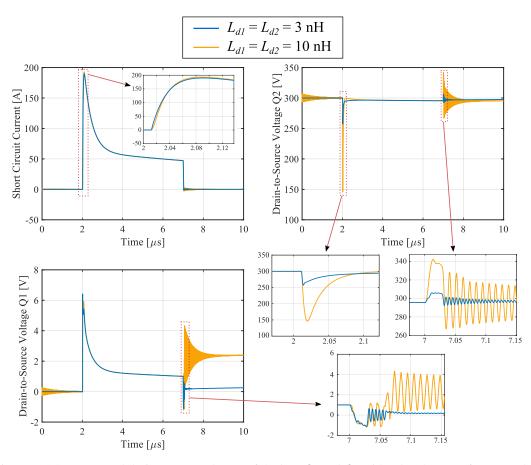

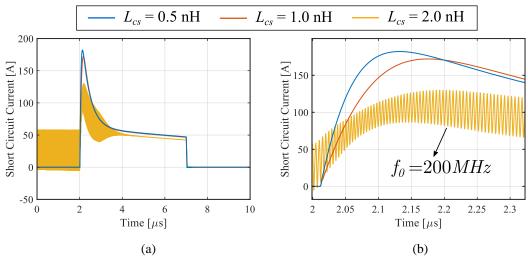

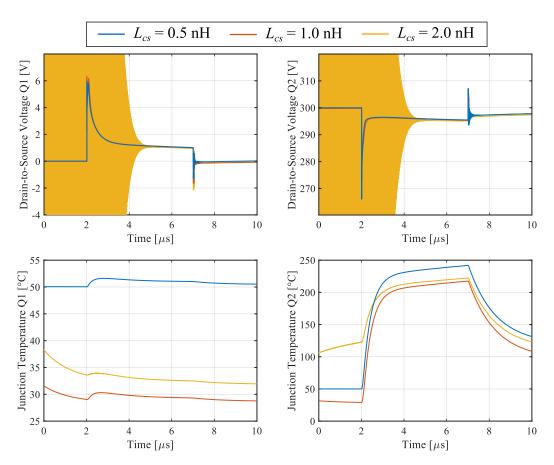

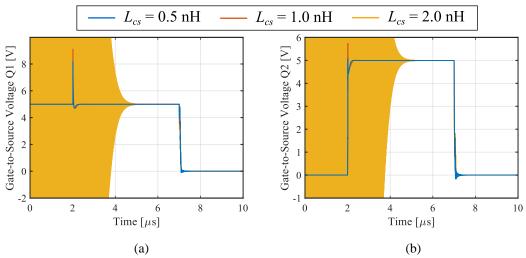

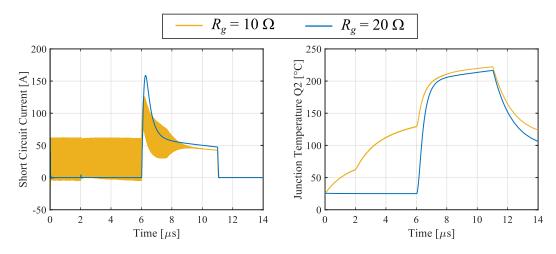

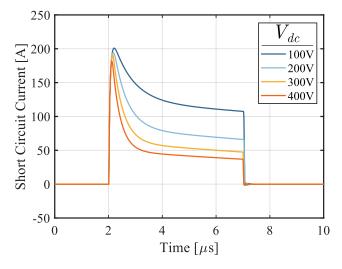

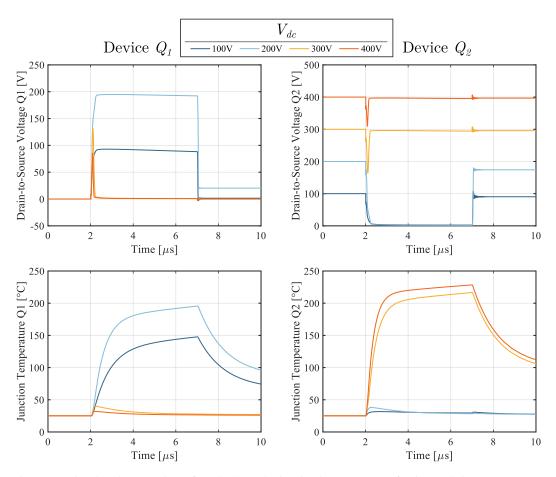

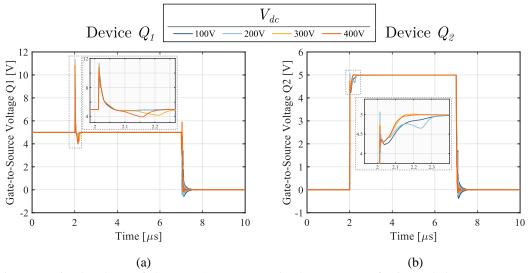

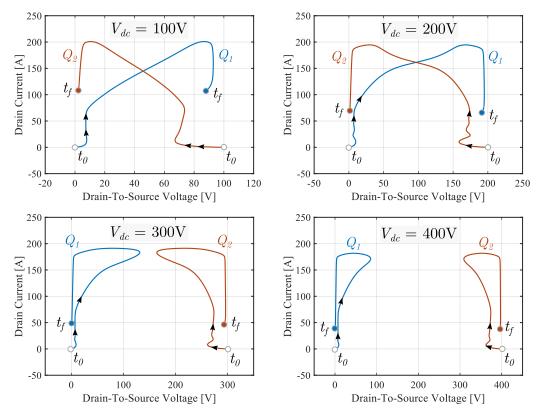

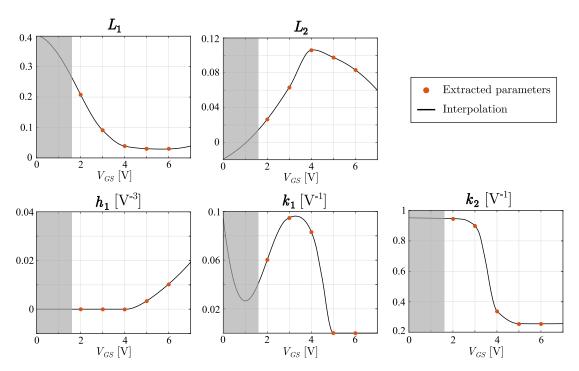

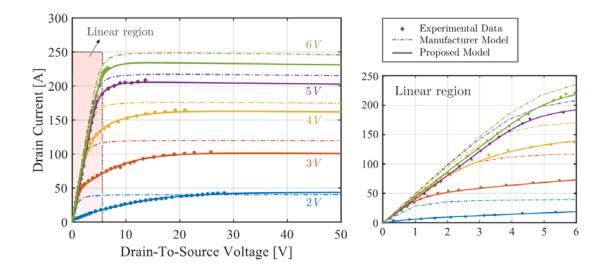

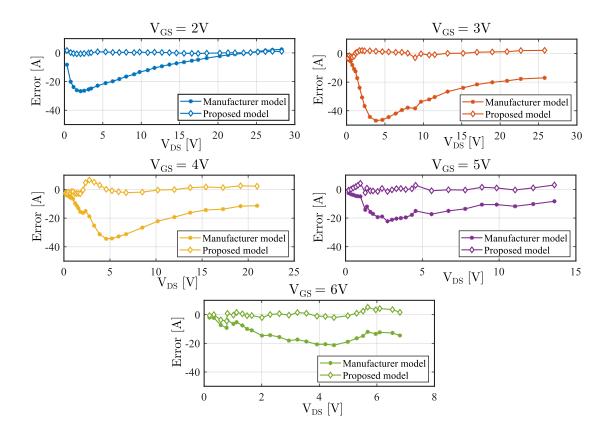

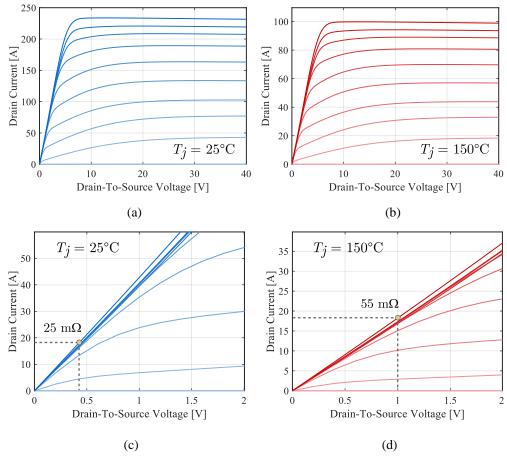

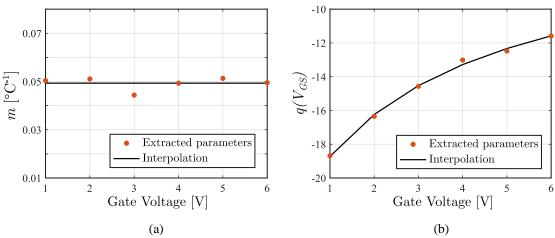

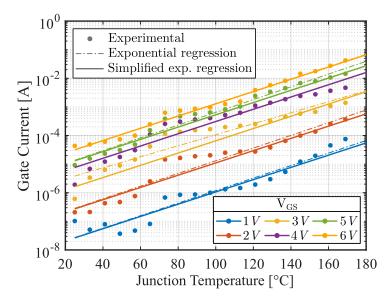

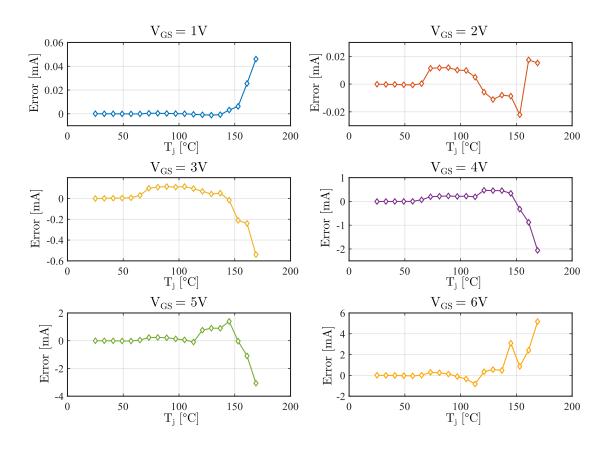

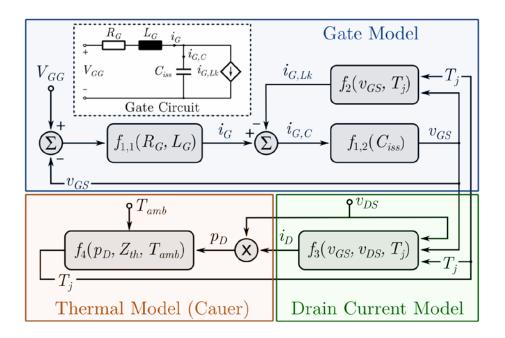

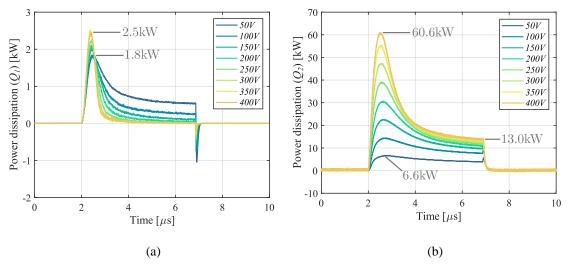

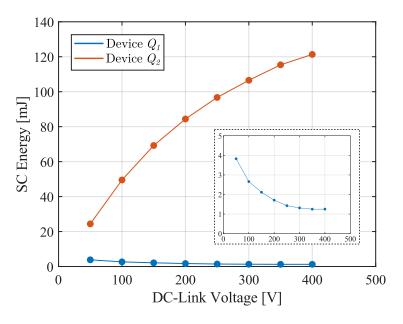

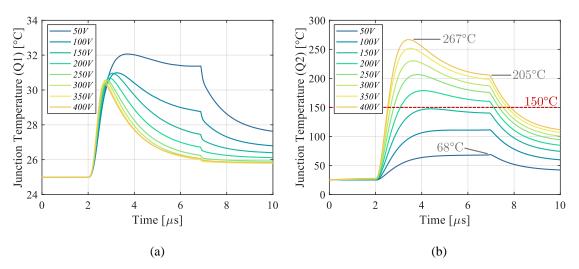

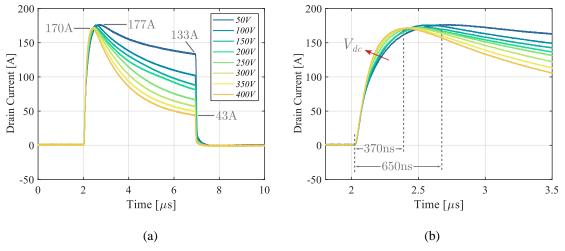

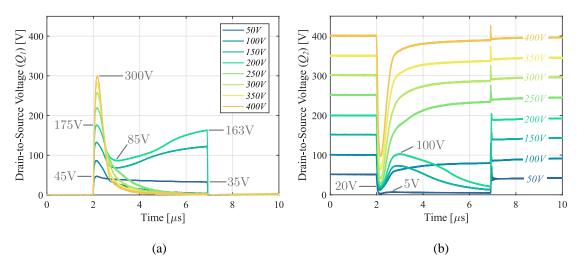

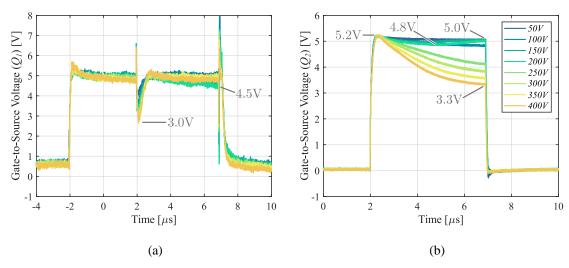

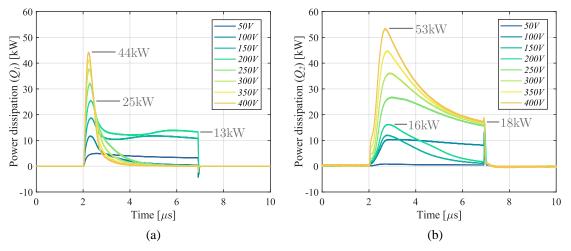

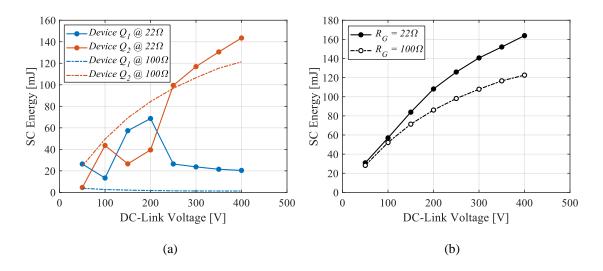

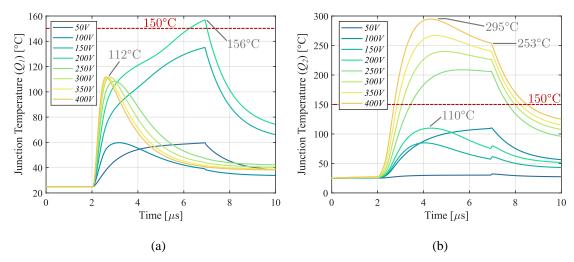

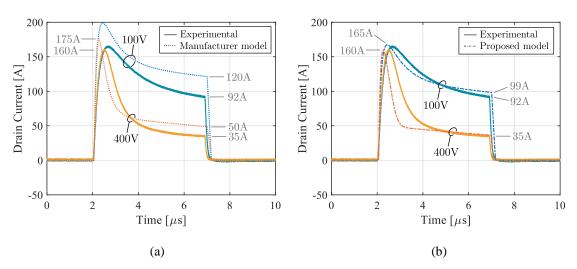

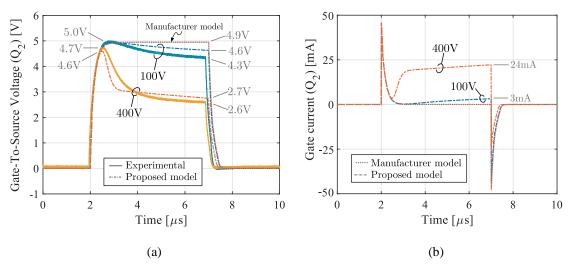

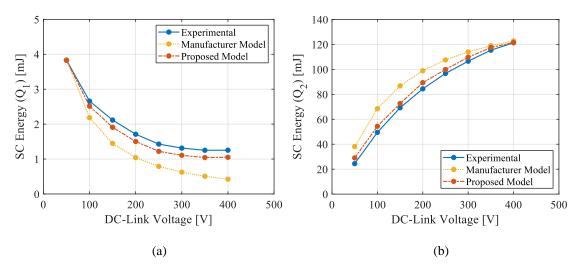

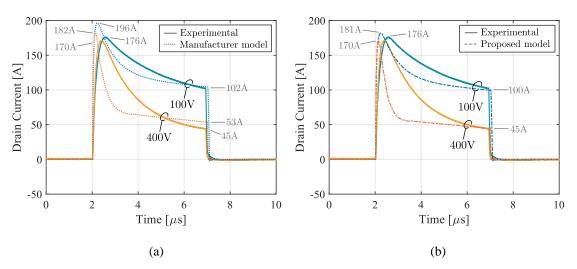

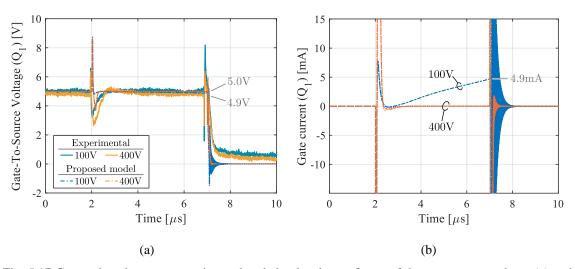

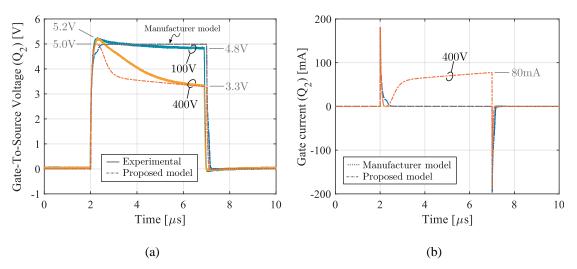

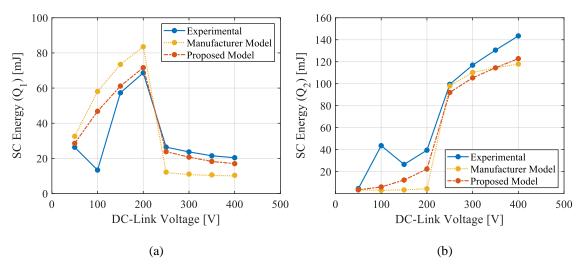

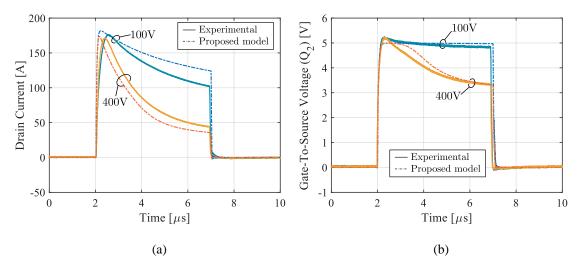

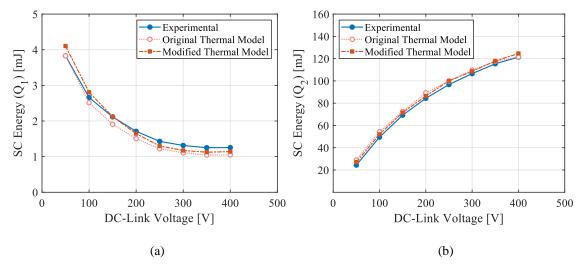

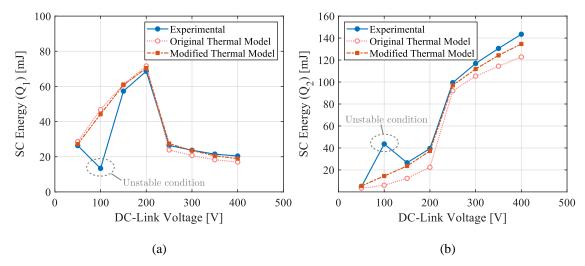

Further insights on the failure mechanisms of 650 V GaN HEMTs under SC conditions are provided in [39]-[41], where two types of failures are identified. The first happens for  $V_{DS} < 350$  V and with long time to failure, involving a huge amount of energy and high  $T_j$  increase. The second failure happens at higher  $V_{DS}$  and occurs in less than 1 µs, involving much lower energy.